Chapter 23 Memory Mapping Control (S12XMMCV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

896 Freescale Semiconductor

The fixed 16K page from $4000–$7FFF (when ROMHM = 0) is the page number $FD.

The reset value of $FE ensures that there is linear Flash space available between addresses $4000 and

$FFFF out of reset.

The fixed 16K page from $C000-$FFFF is the page number $FF.

23.3.2.9 RAM Write Protection Control Register (RAMWPC)

Read: Anytime

Write: Anytime

Table 23-13. PPAGE Field Descriptions

Field Description

7–0

PIX[7:0]

Program Page Index Bits 7–0 — These page index bits are used to select which of the 256 FLASH or ROM

array pages is to be accessed in the Program Page Window.

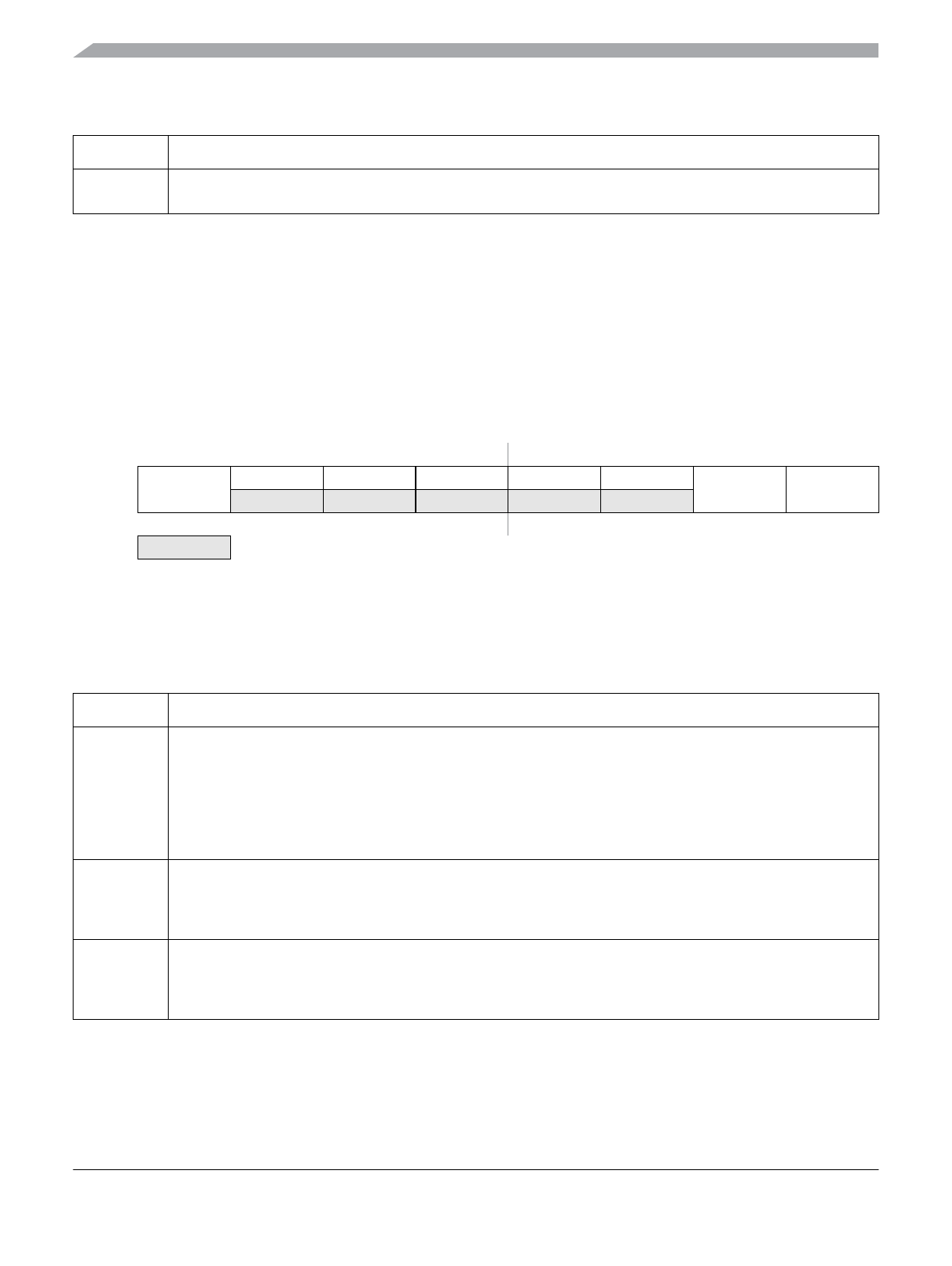

Address: 0x011C

76543210

R

RWPE

00000

AVIE AVIF

W

Reset 00000000

= Unimplemented or Reserved

Figure 23-17. RAM Write Protection Control Register (RAMWPC)

Table 23-14. RAMWPC Field Descriptions

Field Description

7

RWPE

RAM Write Protection Enable — This bit enables the RAM write protection mechanism. When the RWPE bit

is cleared, there is no write protection and any memory location is writable by the CPU module and the XGATE

module. When the RWPE bit is set the write protection mechanism is enabled and write access of the CPU or

to the XGATE RAM region. Write access performed by the XGATE module to outside of the XGATE RAM region

or the shared region is suppressed as well in this case.

0 RAM write protection check is disabled, region boundary registers can be written.

1 RAM write protection check is enabled, region boundary registers cannot be written.

1

AVIE

CPU Access Violation Interrupt Enable — This bit enables the Access Violation Interrupt. If AVIE is set and

AVIF is set, an interrupt is generated.

0 CPU Access Violation Interrupt Disabled.

1 CPU Access Violation Interrupt Enabled.

0

AVIF

CPU Access Violation Interrupt Flag — When set, this bit indicates that the CPU has tried to write a memory

location inside the XGATE RAM region. This flag can be reset by writing’1’ to the AVIF bit location.

0 No access violation by the CPU was detected.

1 Access violation by the CPU was detected.