Chapter 22 External Bus Interface (S12XEBIV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

868 Freescale Semiconductor

22.4 Functional Description

This section describes the functions of the external bus interface. The availability of external signals and

functions in relation to the operating mode is initially summarized and described in more detail in separate

sub-sections.

22.4.1 Operating Modes and External Bus Properties

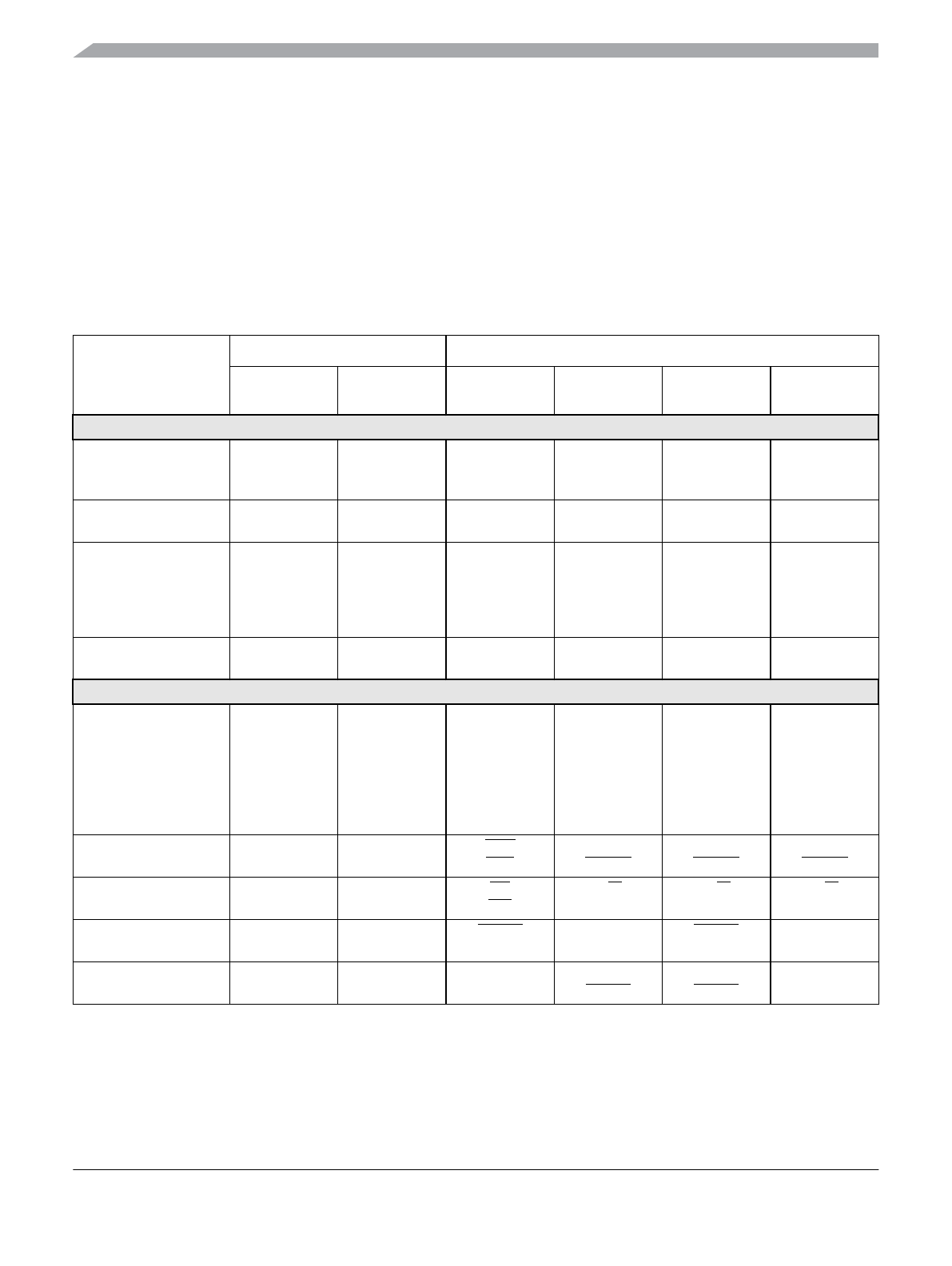

A summary of the external bus interface functions for each operating mode is shown in Table 22-7.

Table 22-7. Summary of Functions

Properties

(if Enabled)

Single-Chip Modes Expanded Modes

Normal

Single-Chip

Special

Single-Chip

Normal

Expanded

Emulation

Single-Chip

Emulation

Expanded

Special

Test

Timing Properties

PRR access

1

1

Incl. S12X_EBI registers

2 cycles

read internal

write internal

2 cycles

read internal

write internal

2 cycles

read internal

write internal

2 cycles

read external

write int & ext

2 cycles

read external

write int & ext

2 cycles

read internal

write internal

Internal access

visible externally

——

—

1 cycle 1 cycle 1 cycle

External

address access

and

unimplemented area

access

2

2

Refer to S12X_MMC section.

— — Max. of 2 to 9

programmed

cycles

or n cycles of

ext. wait

3

3

If EWAITE = 1, the minimum number of external bus cycles is 3.

1 cycle Max. of 2 to 9

programmed

cycles

or n cycles of

ext. wait

3

1 cycle

Flash area

address access

4

4

Available only if configured appropriately by ROMON and EROMON (refer to S12X_MMC section).

— — — 1 cycle 1 cycle 1 cycle

Signal Properties

Bus signals — — ADDR[22:1]

DATA[15:0]

ADDR[22:20]/A

CC[2:0]

ADDR[19:16]/

IQSTAT[3:0]

ADDR[15:0]/

IVD[15:0]

DATA[15:0]

ADDR[22:20]/A

CC[2:0]

ADDR[19:16]/

IQSTAT[3:0]

ADDR[15:0]/

IVD[15:0]

DATA[15:0]

ADDR[22:0]

DATA[15:0]

Data select signals

(if 16-bit data bus)

——

UDS

LDS

ADDR0

LSTRB

ADDR0

LSTRB

ADDR0

LSTRB

Data direction signals — —

RE

WE

R/

WR/WR/W

External wait

feature

——

EWAIT — EWAIT —

Reduced input

threshold enabled on

— — Refer to

Table 22-3

DATA[15:0]

EWAIT

DATA[15:0]

EWAIT

Refer to

Table 22-3