Chapter 16 Serial Peripheral Interface (S12SPIV4)

MC9S12XDP512 Data Sheet, Rev. 2.11

Freescale Semiconductor 721

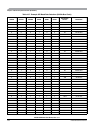

16.3.2.5 SPI Data Register (SPIDR)

Read: Anytime; normally read only when SPIF is set

Write: Anytime

The SPI data register is both the input and output register for SPI data. A write to this register

allows a data byte to be queued and transmitted. For an SPI configured as a master, a queued data

byte is transmitted immediately after the previous transmission has completed. The SPI transmitter

empty flag SPTEF in the SPISR register indicates when the SPI data register is ready to accept new

data.

Received data in the SPIDR is valid when SPIF is set.

If SPIF is cleared and a byte has been received, the received byte is transferred from the receive

shift register to the SPIDR and SPIF is set.

If SPIF is set and not serviced, and a second byte has been received, the second received byte is

kept as valid byte in the receive shift register until the start of another transmission. The byte in the

SPIDR does not change.

If SPIF is set and a valid byte is in the receive shift register, and SPIF is serviced before the start of

a third transmission, the byte in the receive shift register is transferred into the SPIDR and SPIF

remains set (see Figure 16-8).

If SPIF is set and a valid byte is in the receive shift register, and SPIF is serviced after the start of

a third transmission, the byte in the receive shift register has become invalid and is not transferred

into the SPIDR (see Figure 16-9).

Module Base +0x___5

76543210

R

Bit 7 6 5 4 3 2 2 Bit 0

W

Reset 00000000

Figure 16-7. SPI Data Register (SPIDR)