Chapter 20 Debug (S12XDBGV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

Freescale Semiconductor 829

20.4.7.5 DBG Breakpoint Priorities

XGATE software breakpoints have the highest priority. Active tracing sessions are terminated

immediately.

If a TRIG triggers occur after begin or mid aligned tracing has already been triggered by a comparator

instigated transition to final state, then TRIG no longer has an effect. When the associated tracing session

is complete, the breakpoint occurs. Similarly if a TRIG is followed by a subsequent trigger from a

comparator channel whose BRK=0, it has no effect, since tracing has already started.

If a comparator tag hit occurs simultaneously with an external

TAGHI/TAGLO hit, the state sequencer

enters State0.

TAGHI/TAGLO triggers are always end aligned, to end tracing immediately, independent of

the tracing trigger alignment bits TALIGN[1:0].

20.4.7.5.1 DBG Breakpoint priorities, mapping and BDM interfacing

Breakpoint operation is dependent on the state of the BDM module. If the BDM module is active, the CPU

is executing out of BDM firmware and S12X breakpoints are disabled. In addition, while executing a BDM

TRACE command, tagging into BDM is disabled.

If BDM is not active, the breakpoint will give priority to BDM requests over SWI requests if the breakpoint

happens to coincide with a SWI instruction in the user’s code. On returning from BDM, the SWI from user

code gets executed.

BDM cannot be entered from a breakpoint unless the ENABLE bit is set in the BDM. If entry to BDM via

a BGND instruction is attempted and the ENABLE bit in the BDM is cleared, the CPU actually executes

the BDM firmware code. It checks the ENABLE and returns if ENABLE is not set. If not serviced by the

monitor then the breakpoint is re-asserted when the BDM returns to normal CPU flow.

If the comparator register contents coincide with the SWI/BDM vector address then an SWI in user code

and DBG breakpoint could occur simultaneously. The CPU ensures that BDM requests have a higher

priority than SWI requests. Returning from the BDM/SWI service routine care must be taken to avoid

re-triggering a breakpoint.

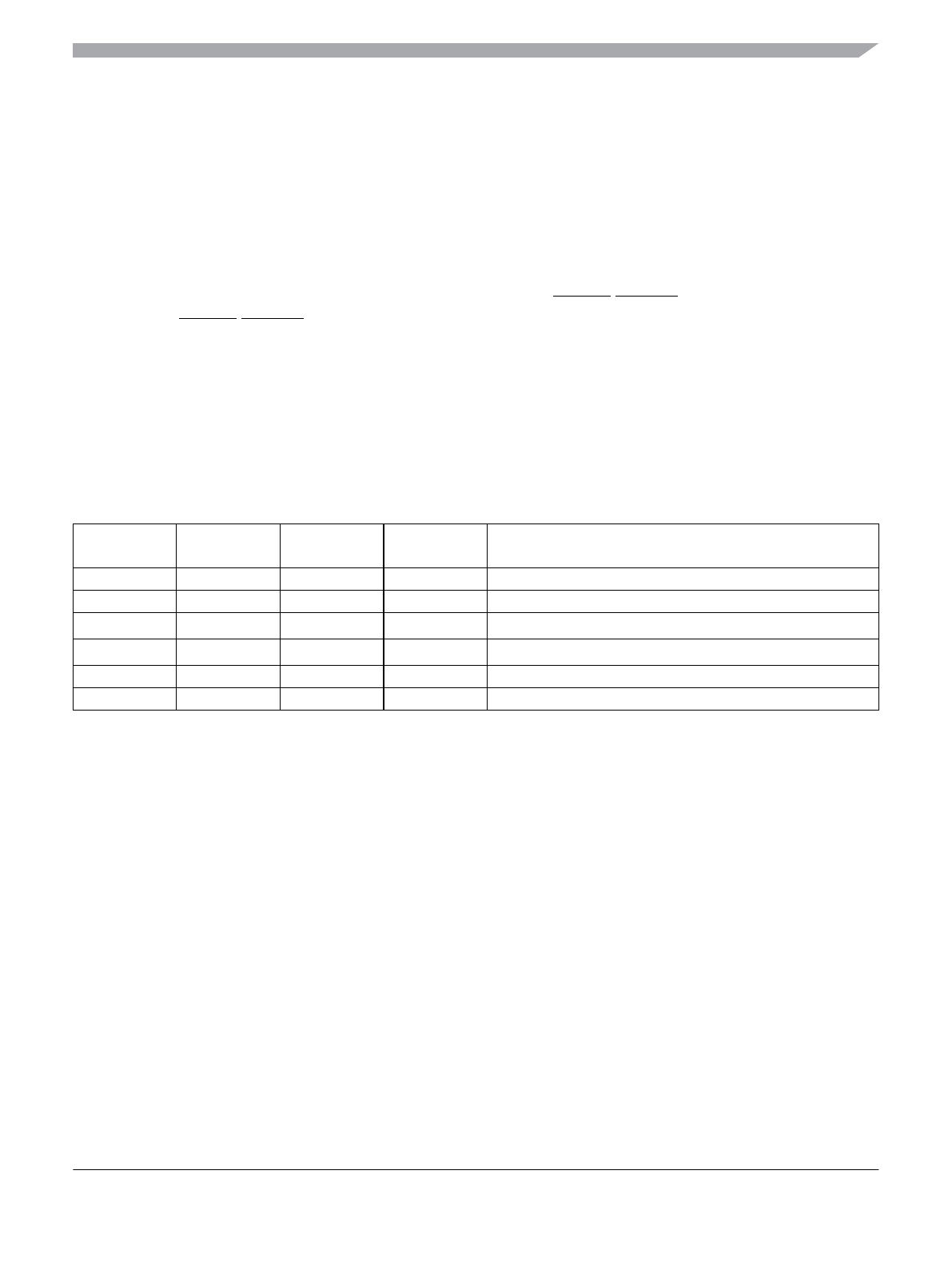

Table 20-45. Breakpoint Mapping Summary

DBGBRK[1]

(DBGC1[3])

1

1

All sources except XGATE software BKP, which are independent of this bit.

BDM bit

(DBGC1[4])

BDM

enabled

BDM active Type of Debug Session

0 X X X No Breakpoint

1000 Breakpoint to SWI

101X

Illegal Configuration. Do Not Use.

2

2

The DBGC1[4] bit (BDM) must be set if using the BDM interface together with the DBG module. Failure to set this bit could

result in XGATE generated breakpoints to SWI during BDM firmware execution corrupting the S12X PC return address,

should the user have entered BDM via the BACKGROUND command or BGND instruction.

1100

Illegal Configuration. Do Not Use.

3

3

End aligned tagged Breakpoint to SWI. Begin, Mid aligned and Forced Breakpoints disabled

1110 Breakpoint to BDM

1111 No Breakpoint