Chapter 15 Serial Communication Interface (S12MC9S12XDP512V5)

MC9S12XDP512 Data Sheet, Rev. 2.11

684 Freescale Semiconductor

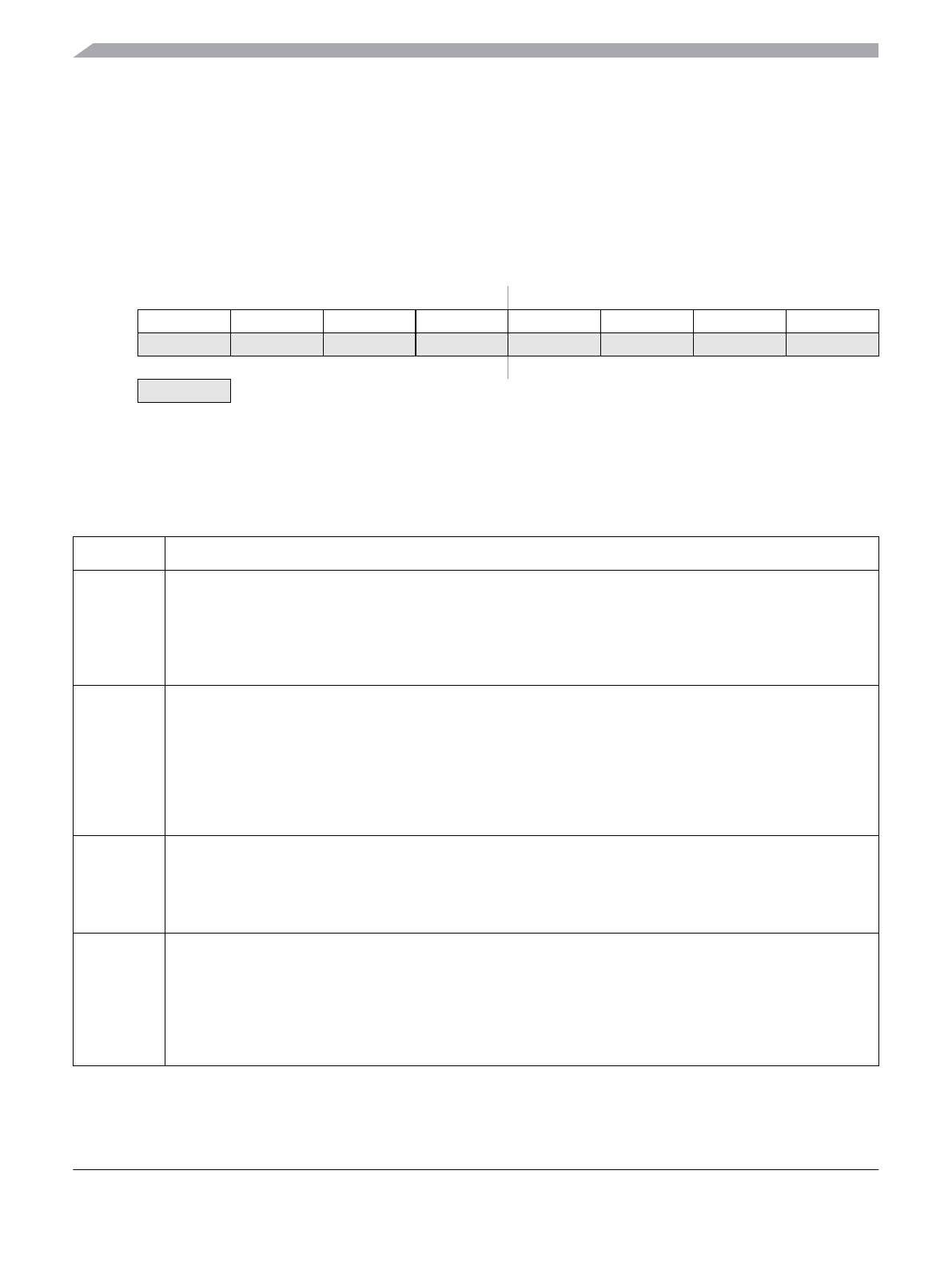

15.3.2.7 SCI Status Register 1 (SCISR1)

The SCISR1 and SCISR2 registers provides inputs to the MCU for generation of SCI interrupts. Also,

these registers can be polled by the MCU to check the status of these bits. The flag-clearing procedures

require that the status register be read followed by a read or write to the SCI data register.It is permissible

to execute other instructions between the two steps as long as it does not compromise the handling of I/O,

but the order of operations is important for flag clearing.

Read: Anytime

Write: Has no meaning or effect

Module Base + 0x0004

76543210

R TDRE TC RDRF IDLE OR NF FE PF

W

Reset 11000000

= Unimplemented or Reserved

Figure 15-10. SCI Status Register 1 (SCISR1)

Table 15-11. SCISR1 Field Descriptions

Field Description

7

TDRE

Transmit Data Register Empty Flag — TDRE is set when the transmit shift register receives a byte from the

SCI data register. When TDRE is 1, the transmit data register (SCIDRH/L) is empty and can receive a new value

to transmit.Clear TDRE by reading SCI status register 1 (SCISR1), with TDRE set and then writing to SCI data

register low (SCIDRL).

0 No byte transferred to transmit shift register

1 Byte transferred to transmit shift register; transmit data register empty

6

TC

Transmit Complete Flag — TC is set low when there is a transmission in progress or when a preamble or break

character is loaded. TC is set high when the TDRE flag is set and no data, preamble, or break character is being

transmitted.When TC is set, the TXD pin becomes idle (logic 1). Clear TC by reading SCI status register 1

(SCISR1) with TC set and then writing to SCI data register low (SCIDRL). TC is cleared automatically when data,

preamble, or break is queued and ready to be sent. TC is cleared in the event of a simultaneous set and clear of

the TC flag (transmission not complete).

0 Transmission in progress

1 No transmission in progress

5

RDRF

Receive Data Register Full Flag — RDRF is set when the data in the receive shift register transfers to the SCI

data register. Clear RDRF by reading SCI status register 1 (SCISR1) with RDRF set and then reading SCI data

register low (SCIDRL).

0 Data not available in SCI data register

1 Received data available in SCI data register

4

IDLE

Idle Line Flag — IDLE is set when 10 consecutive logic 1s (if M = 0) or 11 consecutive logic 1s (if M =1) appear

on the receiver input. Once the IDLE flag is cleared, a valid frame must again set the RDRF flag before an idle

condition can set the IDLE flag.Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then

reading SCI data register low (SCIDRL).

0 Receiver input is either active now or has never become active since the IDLE flag was last cleared

1 Receiver input has become idle

Note: When the receiver wakeup bit (RWU) is set, an idle line condition does not set the IDLE flag.