Chapter 15 Serial Communication Interface (S12MC9S12XDP512V5)

MC9S12XDP512 Data Sheet, Rev. 2.11

680 Freescale Semiconductor

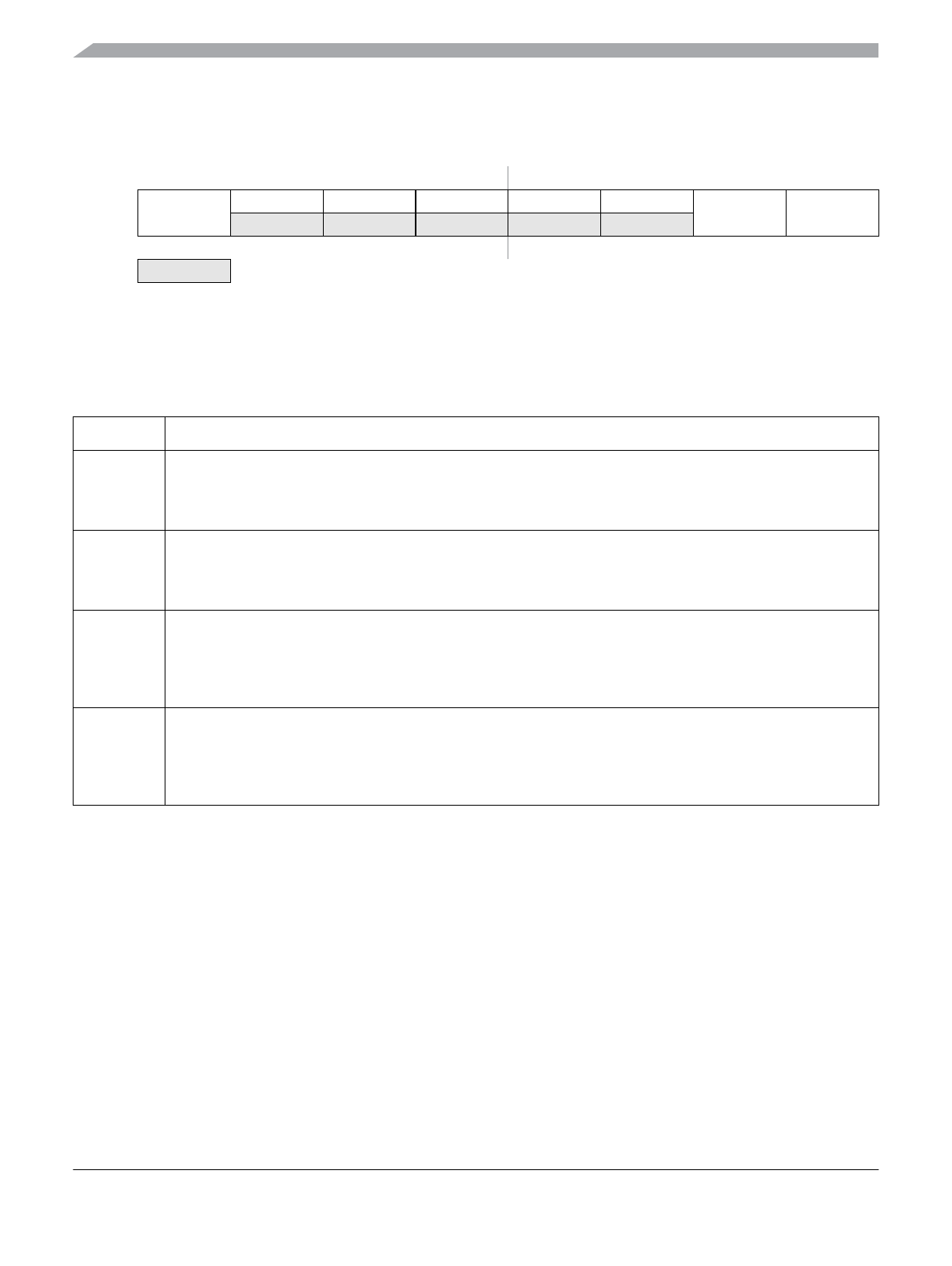

15.3.2.3 SCI Alternative Status Register 1 (SCIASR1)

Read: Anytime, if AMAP = 1

Write: Anytime, if AMAP = 1

Module Base + 0x000a

76543210

R

RXEDGIF

0 0 0 0 BERRV

BERRIF BKDIF

W

Reset 00000000

= Unimplemented or Reserved

Figure 15-6. SCI Alternative Status Register 1 (SCIASR1)

Table 15-6. SCIASR1 Field Descriptions

Field Description

7

RXEDGIF

Receive Input Active Edge Interrupt Flag — RXEDGIF is asserted, if an active edge (falling if RXPOL = 0,

rising if RXPOL = 1) on the RXD input occurs. RXEDGIF bit is cleared by writing a “1” to it.

0 No active receive on the receive input has occurred

1 An active edge on the receive input has occurred

2

BERRV

Bit Error Value — BERRV reflects the state of the RXD input when the bit error detect circuitry is enabled and

a mismatch to the expected value happened. The value is only meaningful, if BERRIF = 1.

0 A low input was sampled, when a high was expected

1 A high input reassembled, when a low was expected

1

BERRIF

Bit Error Interrupt Flag — BERRIF is asserted, when the bit error detect circuitry is enabled and if the value

sampled at the RXD input does not match the transmitted value. If the BERRIE interrupt enable bit is set an

interrupt will be generated. The BERRIF bit is cleared by writing a “1” to it.

0 No mismatch detected

1 A mismatch has occurred

0

BKDIF

Break Detect Interrupt Flag — BKDIF is asserted, if the break detect circuitry is enabled and a break signal is

received.If the BKDIE interrupt enable bit is set an interrupt will be generated. The BKDIF bit is cleared by writing

a “1” to it.

0 No break signal was received

1 A break signal was received