Chapter 5 Clocks and Reset Generator (S12CRGV6)

MC9S12XDP512 Data Sheet, Rev. 2.11

Freescale Semiconductor 279

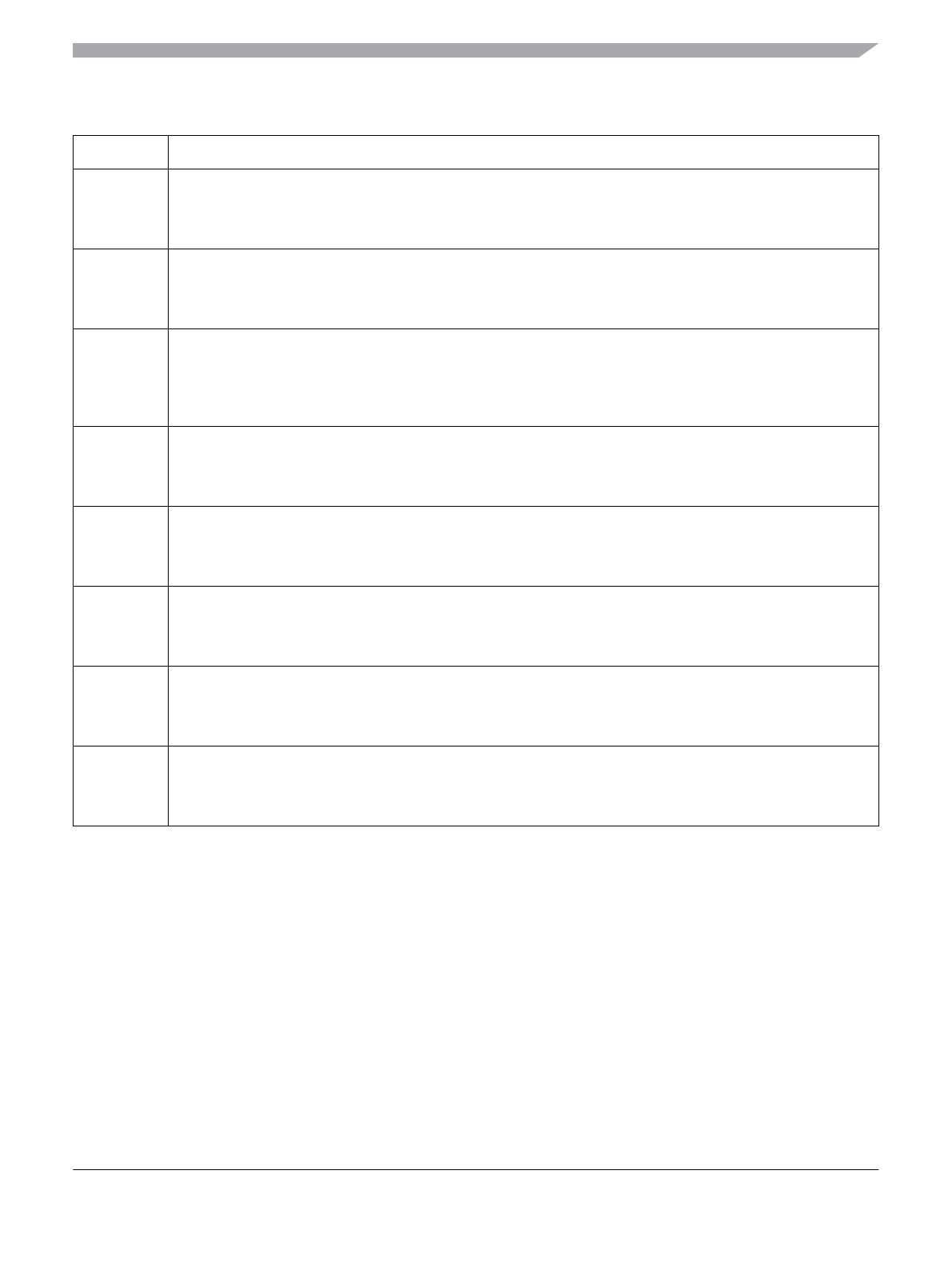

Table 5-2. CRGFLG Field Descriptions

Field Description

7

RTIF

Real Time Interrupt Flag — RTIF is set to 1 at the end of the RTI period. This flag can only be cleared by writing

a 1. Writing a 0 has no effect. If enabled (RTIE = 1), RTIF causes an interrupt request.

0 RTI time-out has not yet occurred.

1 RTI time-out has occurred.

6

PORF

Power on Reset Flag — PORF is set to 1 when a power on reset occurs. This flag can only be cleared by writing

a 1. Writing a 0 has no effect.

0 Power on reset has not occurred.

1 Power on reset has occurred.

5

LVRF

Low Voltage Reset Flag — If low voltage reset feature is not available (see device specification) LVRF always

reads 0. LVRF is set to 1 when a low voltage reset occurs. This flag can only be cleared by writing a 1. Writing

a 0 has no effect.

0 Low voltage reset has not occurred.

1 Low voltage reset has occurred.

4

LOCKIF

PLL Lock Interrupt Flag — LOCKIF is set to 1 when LOCK status bit changes. This flag can only be cleared

by writing a 1. Writing a 0 has no effect.If enabled (LOCKIE = 1), LOCKIF causes an interrupt request.

0 No change in LOCK bit.

1 LOCK bit has changed.

3

LOCK

Lock Status Bit — LOCK reflects the current state of PLL lock condition. This bit is cleared in self clock mode.

Writes have no effect.

0 PLL VCO is not within the desired tolerance of the target frequency.

1 PLL VCO is within the desired tolerance of the target frequency.

2

TRACK

Track Status Bit — TRACK reflects the current state of PLL track condition. This bit is cleared in self clock

mode. Writes have no effect.

0 Acquisition mode status.

1Tracking mode status.

1

SCMIF

Self Clock Mode Interrupt Flag — SCMIF is set to 1 when SCM status bit changes. This flag can only be

cleared by writing a 1. Writing a 0 has no effect. If enabled (SCMIE = 1), SCMIF causes an interrupt request.

0 No change in SCM bit.

1 SCM bit has changed.

0

SCM

Self Clock Mode Status Bit — SCM reflects the current clocking mode. Writes have no effect.

0 MCU is operating normally with OSCCLK available.

1 MCU is operating in self clock mode with OSCCLK in an unknown state. All clocks are derived from PLLCLK

running at its minimum frequency f

SCM

.