Chapter 1 Device Overview (MC9S12XDP512V2)

MC9S12XDP512 Data Sheet, Rev. 2.11

Freescale Semiconductor 75

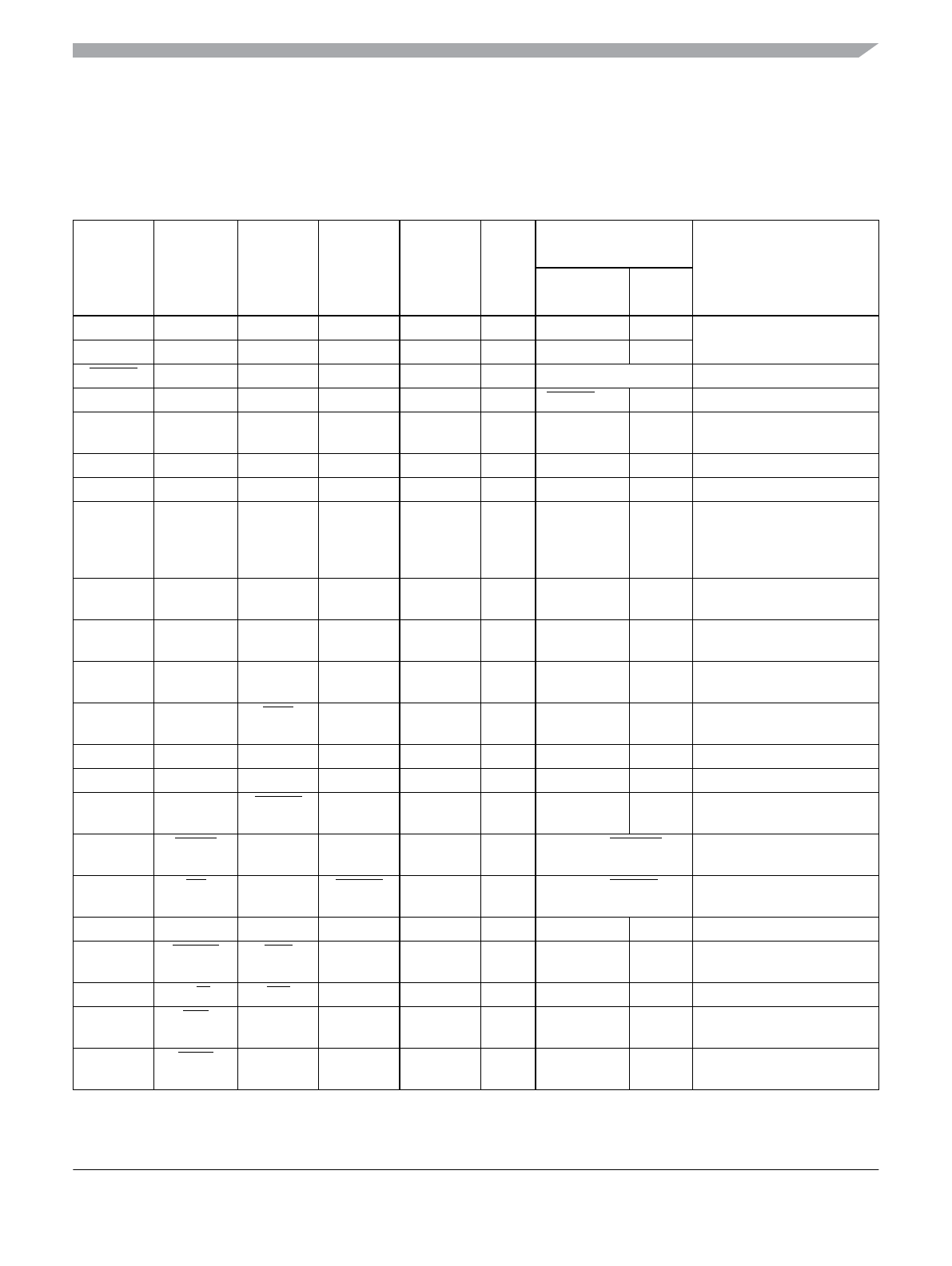

1.2.2 Signal Properties Summary

Table 1-3 summarizes the pin functionality.

Table 1-3. Signal Properties Summary (Sheet 1 of 4)

Pin

Name

Function 1

Pin

Name

Function 2

Pin

Name

Function 3

Pin

Name

Function 4

Pin

Name

Function 5

Power

Supply

Internal Pull

Resistor

Description

CTRL

Reset

State

EXTAL — — — — V

DDPLL

NA NA Oscillator pins

XTAL — — — — V

DDPLL

NA NA

RESET — — — — V

DDR

PULLUP External reset

TEST — — — — N.A.

RESET pin DOWN Test input

V

REGEN

————V

DDX

PUCR Up Voltage regulator enable

Input

XFC — — — — V

DDPLL

NA NA PLL loop filter

BKGD MODC — — — V

DDR

Always on Up Background debug

PAD[23:08] AN[23:8] — — — V

DDA

PER0

AD1/

PER1

AD1

Disabled Port AD inputs of ATD1,

analog inputs of ATD1

PAD[07:00] AN[7:0] — — — V

DDA

PER1

AD0

Disabled Port AD inputs of ATD0,

analog inputs of ATD0

PA[7:0] ADDR[15:8] IVD[15:8] — — V

DDR

PUCR Disabled Port A I/O, address bus,

internal visibility data

PB[7:1] ADDR[7:1] IVD[7:0] — — V

DDR

PUCR Disabled Port B I/O, address bus,

internal visibility data

PB0 ADDR0

UDS V

DDR

PUCR Disabled Port B I/O, address bus,

upper data strobe

PC[7:0] DATA[15:8] — — — V

DDR

PUCR Disabled Port C I/O, data bus

PD[7:0] DATA[7:0] — — — V

DDR

PUCR Disabled Port D I/O, data bus

PE7 ECLKX2

XCLKS — — V

DDR

PUCR Up Port E I/O, system clock

output, clock select

PE6

TAGHI MODB — — V

DDR

While RESET

pin is low: down

Port E I/O, tag high, mode

input

PE5

RE MODA TAGLO — V

DDR

While RESET

pin is low: down

Port E I/O, read enable,

mode input, tag low input

PE4 ECLK — — — V

DDR

PUCR Up Port E I/O, bus clock output

PE3

LSTRB LDS EROMCTL — V

DDR

PUCR Up Port E I/O, low byte data

strobe, EROMON control

PE2 R/

W WE — — V

DDR

PUCR Up Port E I/O, read/write

PE1

IRQ — — — V

DDR

PUCR Up Port E Input, maskable

interrupt

PE0

XIRQ — — — V

DDR

PUCR Up Port E input, non-maskable

interrupt