Chapter 7 Analog-to-Digital Converter (ATD10B16CV4)

MC9S12XDP512 Data Sheet, Rev. 2.11

Freescale Semiconductor 337

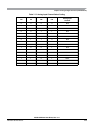

7.3.2.11 ATD Status Register 1 (ATDSTAT1)

This read-only register contains the Conversion Complete Flags CCF7 to CCF0

Read: Anytime

Write: Anytime, no effect

Module Base + 0x000B

76543210

R CCF7 CCF6 CCF5 CCF4 CCF3 CCF2 CCF1 CCF0

W

Reset 00000000

= Unimplemented or Reserved

Figure 7-13. ATD Status Register 1 (ATDSTAT1)

Table 7-22. ATDSTAT1 Field Descriptions

Field Description

7:0

CCF[7:0]

Conversion Complete Flag Bits — A conversion complete flag is set at the end of each conversion in a

conversion sequence. The flags are associated with the conversion position in a sequence (and also the result

register number). Therefore, CCF0 is set when the first conversion in a sequence is complete and the result is

available in result register ATDDR0; CCF1 is set when the second conversion in a sequence is complete and

the result is available in ATDDR1, and so forth. A CCF flag is cleared when one of the following occurs:

• Write to ATDCTL5 (a new conversion sequence is started)

• If AFFC = 0 and read of ATDSTAT1 followed by read of result register ATDDRx

• If AFFC = 1 and read of result register ATDDRx

In case of a concurrent set and clear on CCFx: The clearing by method A) will overwrite the set. The clearing

by methods B) or C) will be overwritten by the set.

Conversion number x not completed

Conversion number x has completed, result ready in ATDDRx