Chapter 5 Clocks and Reset Generator (S12CRGV6)

MC9S12XDP512 Data Sheet, Rev. 2.11

Freescale Semiconductor 299

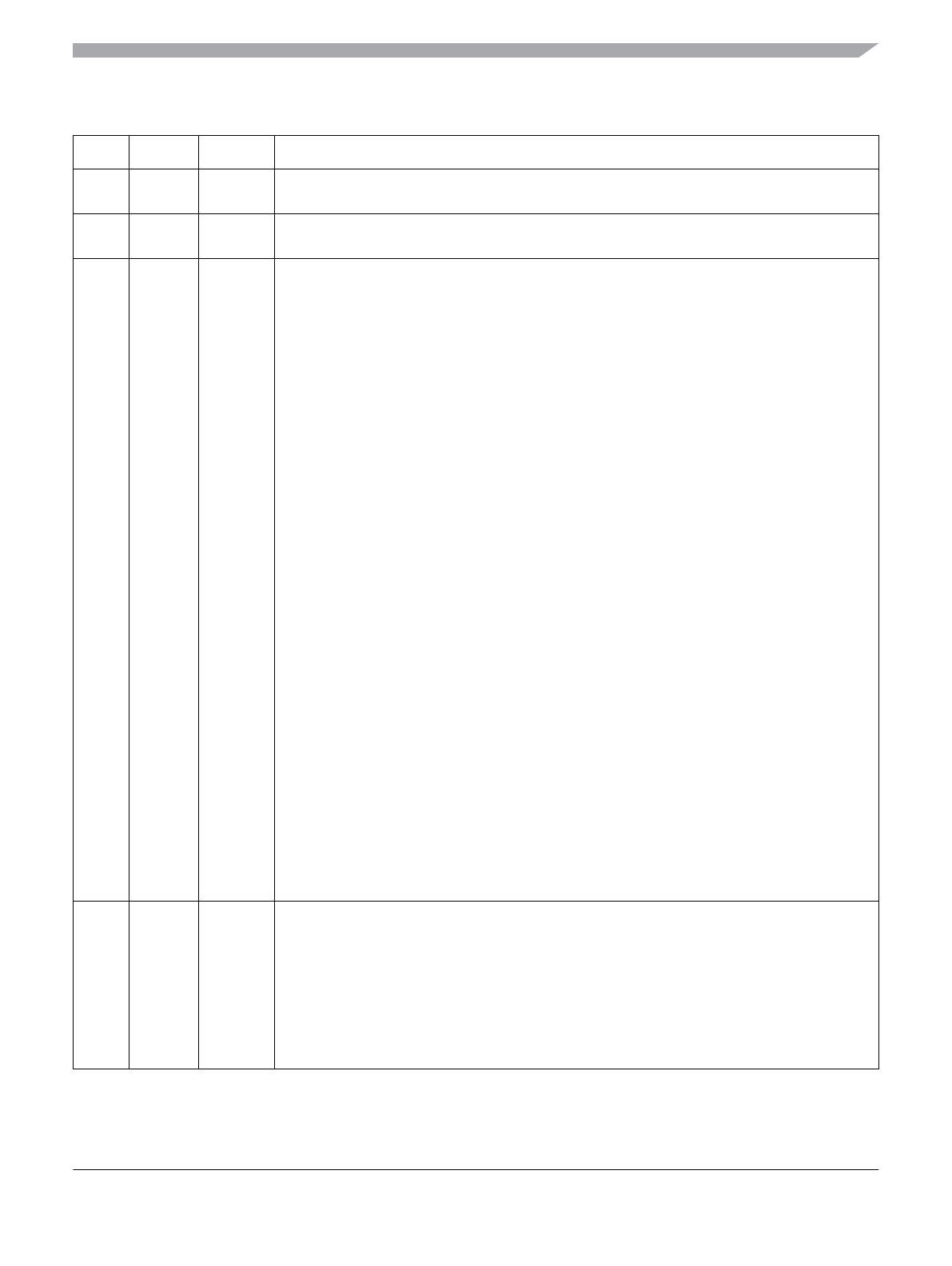

Table 5-12. Outcome of Clock Loss in Wait Mode

CME SCME SCMIE CRG Actions

0X X

Clock failure -->

No action, clock loss not detected.

10 X

Clock failure -->

CRG performs Clock Monitor Reset immediately

11 0

Clock failure -->

Scenario 1: OSCCLK recovers prior to exiting wait mode.

– MCU remains in wait mode,

– VREG enabled,

– PLL enabled,

– SCM activated,

– Start clock quality check,

– Set SCMIF interrupt flag.

Some time later OSCCLK recovers.

– CM no longer indicates a failure,

– 4096 OSCCLK cycles later clock quality check indicates clock o.k.,

– SCM deactivated,

– PLL disabled depending on PLLWAI,

– VREG remains enabled (never gets disabled in wait mode).

– MCU remains in wait mode.

Some time later either a wakeup interrupt occurs (no SCM interrupt)

– Exit wait mode using OSCCLK as system clock (SYSCLK),

– Continue normal operation.

or an External Reset is applied.

– Exit wait mode using OSCCLK as system clock,

– Start reset sequence.

Scenario 2: OSCCLK does not recover prior to exiting wait mode.

– MCU remains in wait mode,

– VREG enabled,

– PLL enabled,

– SCM activated,

– Start clock quality check,

– Set SCMIF interrupt flag,

– Keep performing clock quality checks (could continue infinitely) while in wait mode.

Some time later either a wakeup interrupt occurs (no SCM interrupt)

– Exit wait mode in SCM using PLL clock (f

SCM

) as system clock,

– Continue to perform additional clock quality checks until OSCCLK is o.k. again.

or an External RESET is applied.

– Exit wait mode in SCM using PLL clock (f

SCM

) as system clock,

– Start reset sequence,

– Continue to perform additional clock quality checks until OSCCLKis o.k.again.

11 1

Clock failure -->

– VREG enabled,

– PLL enabled,

– SCM activated,

– Start clock quality check,

– SCMIF set.

SCMIF generates self clock mode wakeup interrupt.

– Exit wait mode in SCM using PLL clock (f

SCM

) as system clock,

– Continue to perform a additional clock quality checks until OSCCLK is o.k. again.