Chapter 18 Periodic Interrupt Timer (S12PIT24B4CV1)

MC9S12XDP512 Data Sheet, Rev. 2.11

760 Freescale Semiconductor

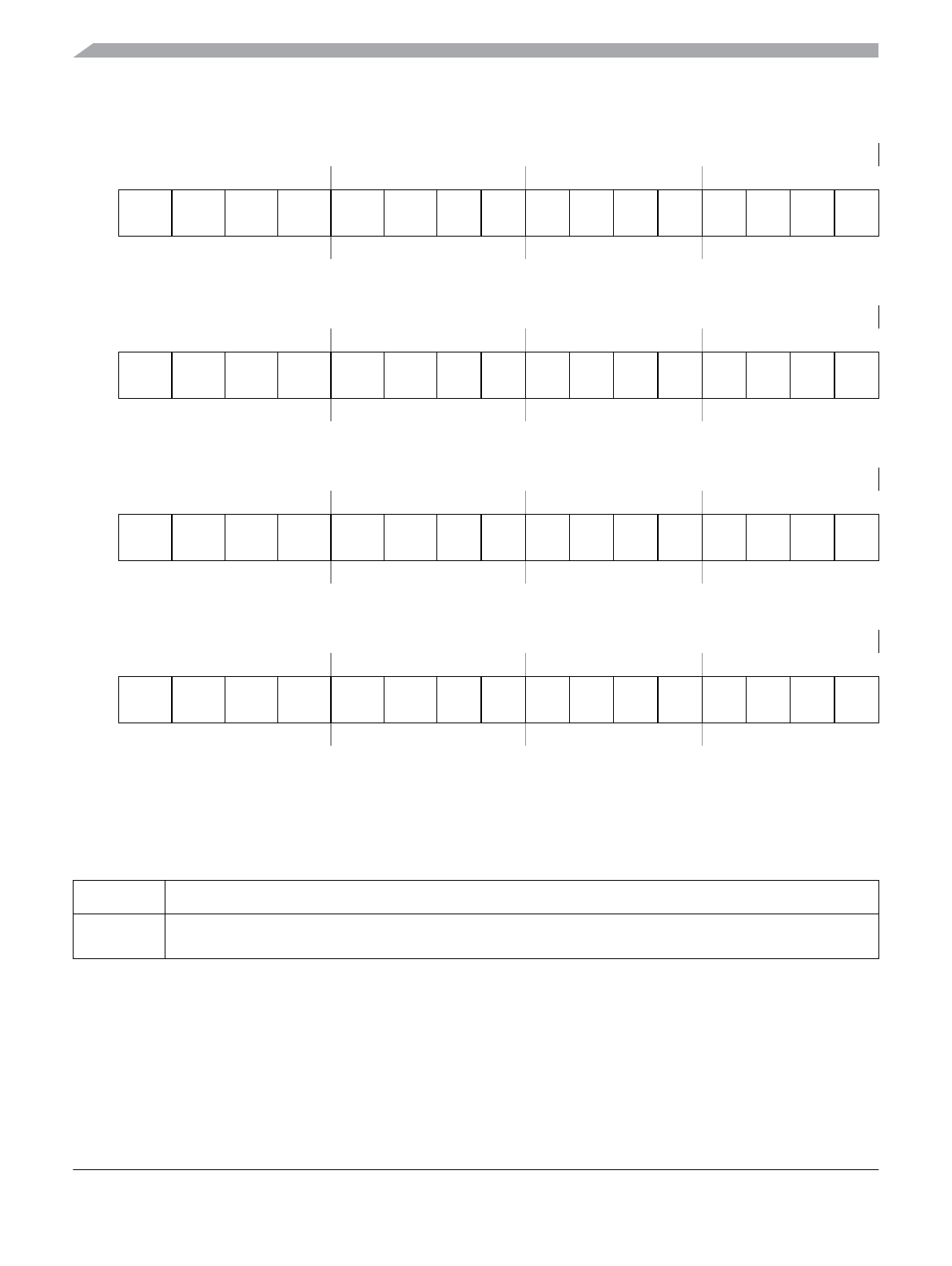

18.3.2.9 PIT Count Register 0 to 3 (PITCNT0–3)

Read: Anytime

Write: Has no meaning or effect

Module Base + 0x000A, 0x000B

151413 1211 109876543210

R

PCNT

15

PCNT

14

PCNT

13

PCNT

12

PCNT

11

PCNT

10

PCNT

9

PCNT

8

PCNT

7

PCNT

6

PCNT

5

PCNT

4

PCNT

3

PCNT

2

PCNT

1

PCNT

0

W

Reset 0000000000000000

Figure 18-15. PIT Count Register 0 (PITCNT0)

Module Base + 0x000E, 0x000F

151413 1211 109876543210

R

PCNT

15

PCNT

14

PCNT

13

PCNT

12

PCNT

11

PCNT

10

PCNT

9

PCNT

8

PCNT

7

PCNT

6

PCNT

5

PCNT

4

PCNT

3

PCNT

2

PCNT

1

PCNT

0

W

Reset 0000000000000000

Figure 18-16. PIT Count Register 1 (PITCNT1)

Module Base + 0x0012, 0x0013

151413 1211 109876543210

R

PCNT

15

PCNT

14

PCNT

13

PCNT

12

PCNT

11

PCNT

10

PCNT

9

PCNT

8

PCNT

7

PCNT

6

PCNT

5

PCNT

4

PCNT

3

PCNT

2

PCNT

1

PCNT

0

W

Reset 0000000000000000

Figure 18-17. PIT Count Register 2 (PITCNT2)

Module Base + 0x0016, 0x0017

151413 1211 109876543210

R

PCNT

15

PCNT

14

PCNT

13

PCNT

12

PCNT

11

PCNT

10

PCNT

9

PCNT

8

PCNT

7

PCNT

6

PCNT

5

PCNT

4

PCNT

3

PCNT

2

PCNT

1

PCNT

0

W

Reset 0000000000000000

Figure 18-18. PIT Count Register 3 (PITCNT3)

Table 18-10. PITCNT0–3 Field Descriptions

Field Description

15:0

PCNT[15:0]

PIT Count Bits 15-0 — These bits represent the current 16-bit modulus down-counter value. The read access

for the count register must take place in one clock cycle as a 16-bit access.