Chapter 9 XGATE (S12XGATEV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

386 Freescale Semiconductor

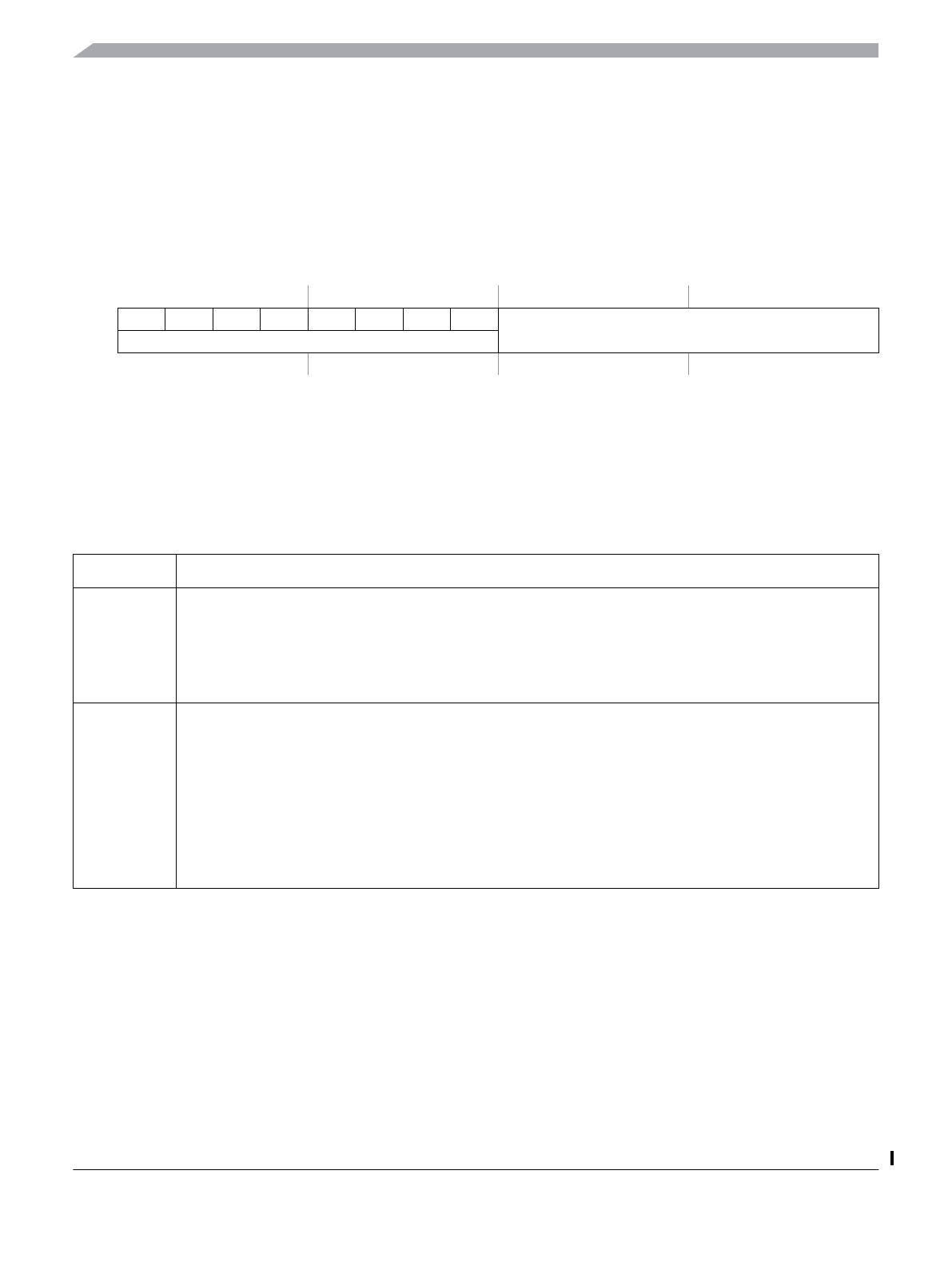

9.3.2.6 XGATE Semaphore Register (XGSEM)

The XGATE provides a set of eight hardware semaphores that can be shared between the S12X_CPU and

the XGATE RISC core. Each semaphore can either be unlocked, locked by the S12X_CPU or locked by

the RISC core. The RISC core is able to lock and unlock a semaphore through its SSEM and CSEM

instructions. The S12X_CPU has access to the semaphores through the XGATE semaphore register

(Figure 9-8). Refer to section Section 9.4.4, “Semaphores” for details.

Read: Anytime

Write: Anytime (see Section 9.4.4, “Semaphores”)

Module Base +0x0001A

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R00000000

XGSEM[7:0]

W XGSEMM[7:0]

Reset 0 0 0 0000000000000

Figure 9-8. XGATE Semaphore Register (XGSEM)

Table 9-7. XGSEM Field Descriptions

Field Description

15–8

XGSEMM[7:0]

Semaphore Mask — These bits control the write access to the XGSEM bits.

Read:

These bits will always read "0".

Write:

0 Disable write access to the XGSEM in the same bus cycle

1 Enable write access to the XGSEM in the same bus cycle

7–0

XGSEM[7:0]

Semaphore Bits — These bits indicate whether a semaphore is locked by the S12X_CPU. A semaphore can

be attempted to be set by writing a "1" to the XGSEM bit and to the corresponding XGSEMM bit in the same

write access. Only unlocked semaphores can be set. A semaphore can be cleared by writing a "0" to the

XGSEM bit and a "1" to the corresponding XGSEMM bit in the same write access.

Read:

0 Semaphore is unlocked or locked by the RISC core

1 Semaphore is locked by the S12X_CPU

Write:

0 Clear semaphore if it was locked by the S12X_CPU

1 Attempt to lock semaphore by the S12X_CPU