Chapter 19 Background Debug Module (S12XBDMV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

Freescale Semiconductor 783

compared to the serial communication rate. This protocol allows a great flexibility for the POD designers,

since it does not rely on any accurate time measurement or short response time to any event in the serial

communication.

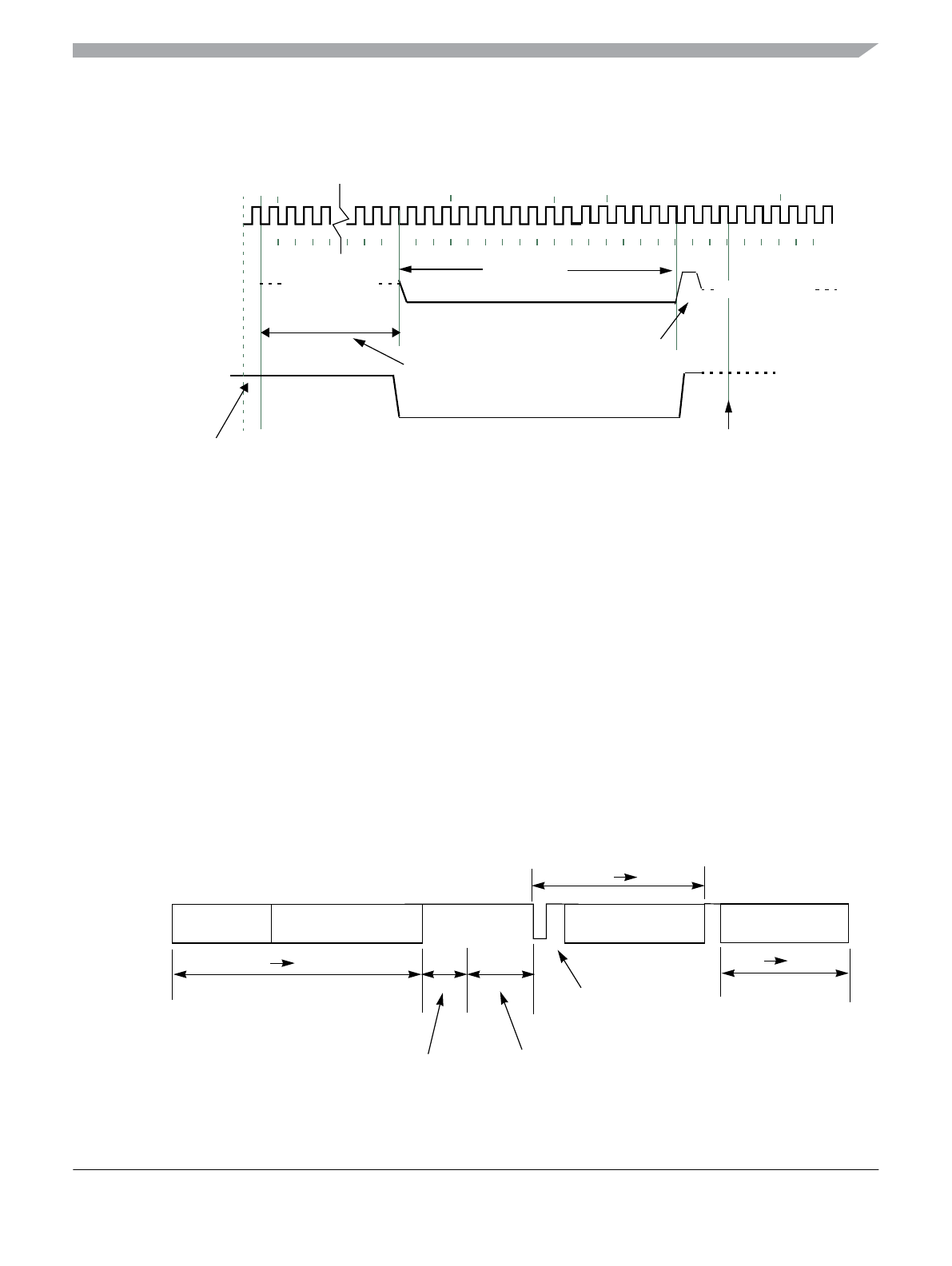

Figure 19-11. Target Acknowledge Pulse (ACK)

NOTE

If the ACK pulse was issued by the target, the host assumes the previous

command was executed. If the CPU enters wait or stop prior to executing a

hardware command, the ACK pulse will not be issued meaning that the

BDM command was not executed. After entering wait or stop mode, the

BDM command is no longer pending.

Figure 19-12 shows the ACK handshake protocol in a command level timing diagram. The READ_BYTE

instruction is used as an example. First, the 8-bit instruction opcode is sent by the host, followed by the

address of the memory location to be read. The target BDM decodes the instruction. A bus cycle is grabbed

(free or stolen) by the BDM and it executes the READ_BYTE operation. Having retrieved the data, the

BDM issues an ACK pulse to the host controller, indicating that the addressed byte is ready to be retrieved.

After detecting the ACK pulse, the host initiates the byte retrieval process. Note that data is sent in the form

of a word and the host needs to determine which is the appropriate byte based on whether the address was

odd or even.

Figure 19-12. Handshake Protocol at Command Level

16 Cycles

BDM Clock

(Target MCU)

Target

Transmits

ACK Pulse

High-Impedance

BKGD Pin

Minimum Delay

From the BDM Command

32 Cycles

Earliest

Start of

Next Bit

Speedup Pulse

16th Tick of the

Last Command Bit

High-Impedance

READ_BYTE

BDM Issues the

BKGD Pin

Byte Address

BDM Executes the

READ_BYTE Command

Host Target

HostTarget

BDM Decodes

the Command

ACK Pulse (out of scale)

Host Target

(2) Bytes are

Retrieved

New BDM

Command