Chapter 22 External Bus Interface (S12XEBIV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

872 Freescale Semiconductor

22.4.2.2.3 Read-Write-Read Access Timing

22.4.2.3 Internal Visibility Data

Depending on the access size and alignment, either a word of read data is made visible on the address lines

or only the related data byte will be presented in the ECLK low phase. For details refer to Table 22-16.

22.4.3 Accesses to Port Replacement Registers

All read and write accesses to PRR addresses take two bus clock cycles independent of the operating mode.

If writing to these addresses in emulation modes, the access is directed to both, the internal register and

the external resource while reads will be treated external.

The MC9S12XDP512 control registers also belong to this category.

22.4.4 Stretched External Bus Accesses

In order to allow fast internal bus cycles to coexist in a system with slower external resources, the

MC9S12XDP512 supports stretched external bus accesses (wait states).

This feature is available in normal expanded mode and emulation expanded mode for accesses to all

external addresses except emulation memory and PRR. In these cases the fixed access times are 1 or 2

cycles, respectively.

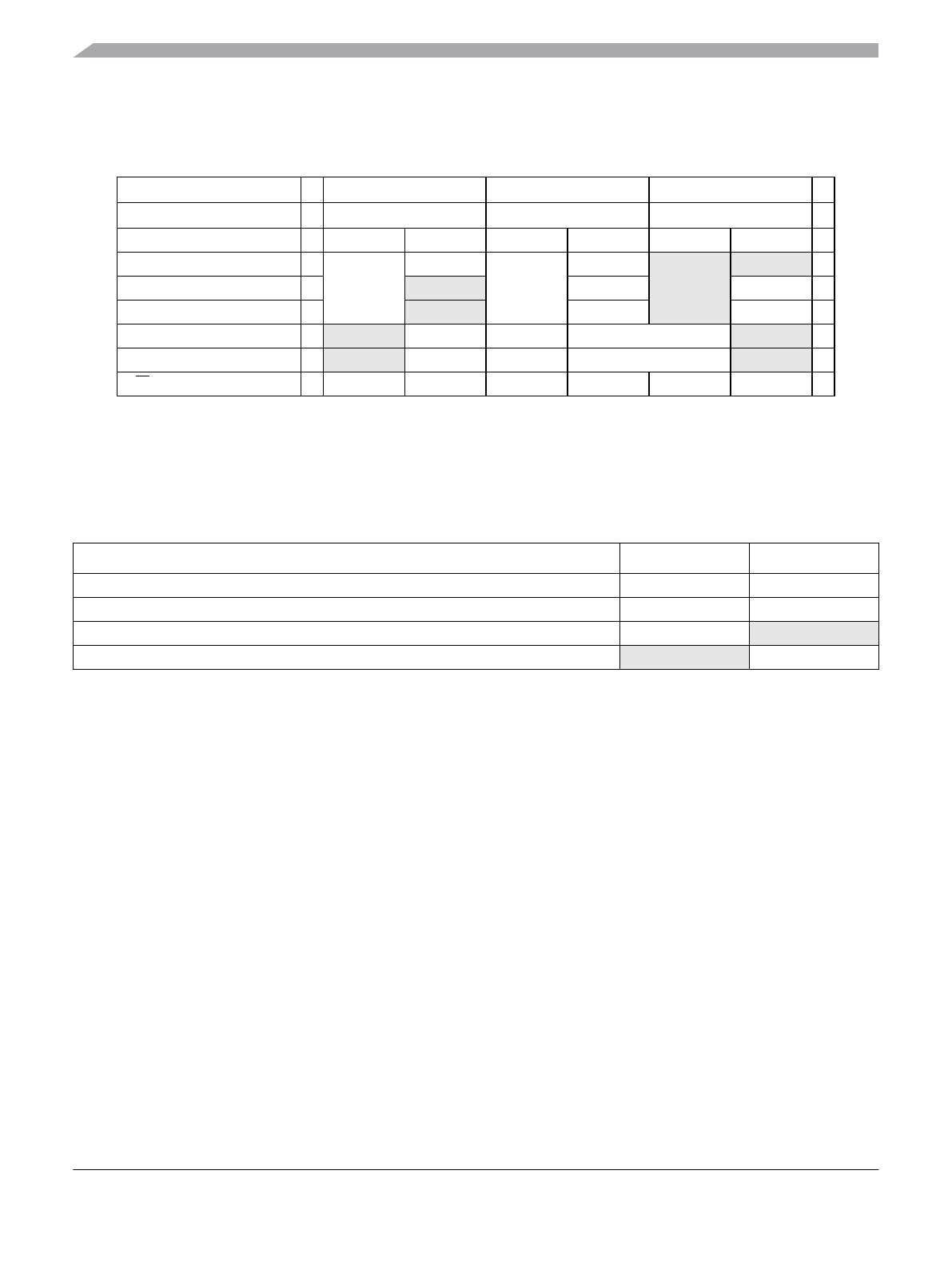

Table 22-15. Interleaved Read-Write-Read Accesses (1 Cycle)

Access #0 Access #1 Access #2

Bus cycle ->

...

123

...

ECLK phase ... high low high low high low ...

ADDR[22:20] / ACC[2:0] ...

addr 0

acc 0

addr 1

acc 1

addr 2

acc 2 ...

ADDR[19:16] / IQSTAT[3:0] ...

iqstat -1 iqstat 0 iqstat 1 ...

ADDR[15:0] / IVD[15:0] ...

? ivd 0 x ...

DATA[15:0] (internal read) ...

? zz(write) data 1 z ...

DATA[15:0] (external read) ...

? z data 0 (write) data 1 z ...

R/

W ... 1 1 0 0 1 1 ...

Table 22-16. IVD Read Data Output

Access IVD[15:8] IVD[7:0]

Word read of data at an even and even+1 address ivd(even) ivd(even+1)

Word read of data at an odd and odd+1 internal RAM address (misaligned) ivd(odd+1) ivd(odd)

Byte read of data at an even address ivd(even)

addr[7:0] (rep.)

Byte read of data at an odd address

addr[15:8] (rep.) ivd(odd)