Chapter 18 Periodic Interrupt Timer (S12PIT24B4CV1)

MC9S12XDP512 Data Sheet, Rev. 2.11

754 Freescale Semiconductor

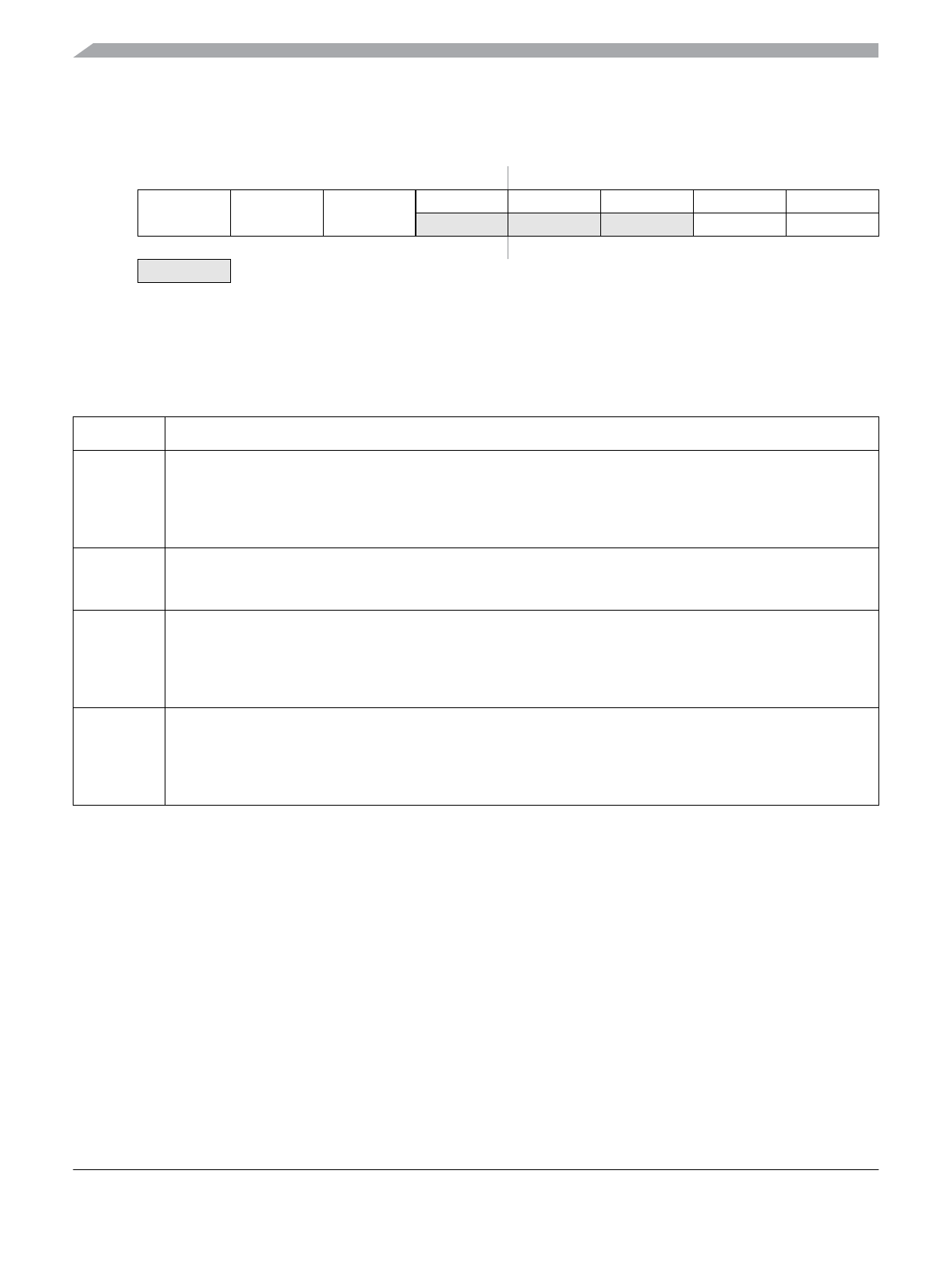

18.3.2.1 PIT Control and Force Load Micro Timer Register (PITCFLMT)

Read: Anytime

Write: Anytime; writes to the reserved bits have no effect

Module Base + 0x0000

76543210

R

PITE PITSWAI PITFRZ

00000

W

PFLMT1 PFLMT0

Reset 00000000

= Unimplemented or Reserved

Figure 18-3. PIT Control and Force Load Micro Timer Register (PITCFLMT)

Table 18-2. PITCFLMT Field Descriptions

Field Description

7

PITE

PIT Module Enable Bit — This bit enables the PIT module. If PITE is cleared, the PIT module is disabled and

flag bits in the PITTF register are cleared. When PITE is set, individually enabled timers (PCE set) start

down-counting with the corresponding load register values.

0 PIT disabled (lower power consumption).

1 PIT is enabled.

6

PITSWAI

PIT Stop in Wait Mode Bit — This bit is used for power conservation while in wait mode.

0 PIT operates normally in wait mode

1 PIT clock generation stops and freezes the PIT module when in wait mode

5

PITFRZ

PIT Counter Freeze while in Freeze Mode Bit — When during debugging a breakpoint (freeze mode) is

encountered it is useful in many cases to freeze the PIT counters to avoid e.g. interrupt generation. The PITFRZ

bit controls the PIT operation while in freeze mode.

0 PIT operates normally in freeze mode

1 PIT counters are stalled when in freeze mode

1:0

PFLMT[1:0]

PIT Force Load Bits for Micro Timer 1:0 — These bits have only an effect if the corresponding micro timer is

active and if the PIT module is enabled (PITE set). Writing a one into a PFLMT bit loads the corresponding 8-bit

micro timer load register into the 8-bit micro timer down-counter. Writing a zero has no effect. Reading these bits

will always return zero.

Note: A micro timer force load affects all timer channels that use the corresponding micro time base.