Chapter 9 XGATE (S12XGATEV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

482 Freescale Semiconductor

9.9 Initialization and Application Information

9.9.1 Initialization

The recommended initialization of the XGATE is as follows:

1. Clear the XGE bit to suppress any incoming service requests.

2. Make sure that no thread is running on the XGATE. This can be done in several ways:

a) Poll the XGCHID register until it reads $00. Also poll XGDBG and XGSWEIF to make sure

that the XGATE has not been stopped.

b) Enter Debug Mode by setting the XGDBG bit. Clear the XGCHID register. Clear the XGDBG

bit.

The recommended method is a).

3. Set the XGVBR register to the lowest address of the XGATE vector space.

4. Clear all Channel ID flags.

5. Copy XGATE vectors and code into the RAM.

6. Initialize the S12X_INT module.

7. Enable the XGATE by setting the XGE bit.

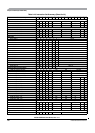

The following code example implements the XGATE initialization sequence.

9.9.2 Code Example (Transmit "Hello World!" on SCI)

CPU S12

;###########################################

;# SYMBOLS #

;###########################################

SCI_REGS EQU $00C8 ;SCI register space

SCIBDH EQU SCI_REGS+$00 ;SCI Baud Rate Register

SCICR2 EQU SCI_REGS+$03 ;SCI Control Register 2

SCISR1 EQU SCI_REGS+$04 ;SCI Status Register 1

SCIDRL EQU SCI_REGS+$07 ;SCI Control Register 2

TIE EQU $80 ;TIE bit mask

TE EQU $08 ;TE bit mask

RE EQU $04 ;RE bit mask

SCI_VEC EQU $D6 ;SCI vector number

INT_REGS EQU $0120 ;S12X_INT register space

INT_CFADDR EQU INT_REGS+$07 ;Interrupt Configuration Address Register

INT_CFDATA EQU INT_REGS+$08 ;Interrupt Configuration Data Registers

RQST EQU $80 ;RQST bit mask

XGATE_REGS EQU $0380 ;XGATE register space

XGMCTL EQU XGATE_REGS+$00 ;XGATE Module Control Register

XGMCTL_CLEAR EQU $F902

XGEM EQU $8000

XGDBGM EQU $2000

XGE EQU $0080

XGDBG EQU $0020

XGSWEIF EQU $0002