Chapter 5 Clocks and Reset Generator (S12CRGV6)

MC9S12XDP512 Data Sheet, Rev. 2.11

286 Freescale Semiconductor

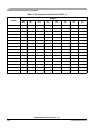

5.3.2.9 CRG COP Control Register (COPCTL)

This register controls the COP (computer operating properly) watchdog.

Read: Anytime

Write:

1. RSBCK: Anytime in special modes; write to “1” but not to “0” in all other modes

2. WCOP, CR2, CR1, CR0:

— Anytime in special modes

— Write once in all other modes

Writing CR[2:0] to “000” has no effect, but counts for the “write once” condition.

Writing WCOP to “0” has no effect, but counts for the “write once” condition.

The COP time-out period is restarted if one these two conditions is true:

1. Writing a nonzero value to CR[2:0] (anytime in special modes, once in all other modes) with

WRTMASK = 0.

or

2. Changing RSBCK bit from “0” to “1”.

Module Base +0x_08

76543210

R

WCOP RSBCK

000

CR2 CR1 CR0

W WRTMASK

Reset

1

0000

1. Refer to Device User Guide (Section: CRG) for reset values of WCOP, CR2, CR1, and CR0.

= Unimplemented or Reserved

Figure 5-12. CRG COP Control Register (COPCTL)

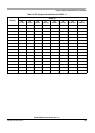

Table 5-9. COPCTL Field Descriptions

Field Description

7

WCOP

Window COP Mode Bit — When set, a write to the ARMCOP register must occur in the last 25% of the selected

period. A write during the first 75% of the selected period will reset the part. As long as all writes occur during

this window, 0x_55 can be written as often as desired. Once 0x_AA is written after the 0x_55, the time-out logic

restarts and the user must wait until the next window before writing to ARMCOP. Table 5-10 shows the duration

of this window for the seven available COP rates.

0 Normal COP operation

1 Window COP operation

6

RSBCK

COP and RTI Stop in Active BDM Mode Bit

0 Allows the COP and RTI to keep running in active BDM mode.

1 Stops the COP and RTI counters whenever the part is in active BDM mode.