Chapter 12 Pulse-Width Modulator (S12PWM8B8CV1)

MC9S12XDP512 Data Sheet, Rev. 2.11

578 Freescale Semiconductor

Write: Anytime

12.3.2.15 PWM Shutdown Register (PWMSDN)

The PWMSDN register provides for the shutdown functionality of the PWM module in the emergency

cases. For proper operation, channel 7 must be driven to the active level for a minimum of two bus clocks.

Read: Anytime

Write: Anytime

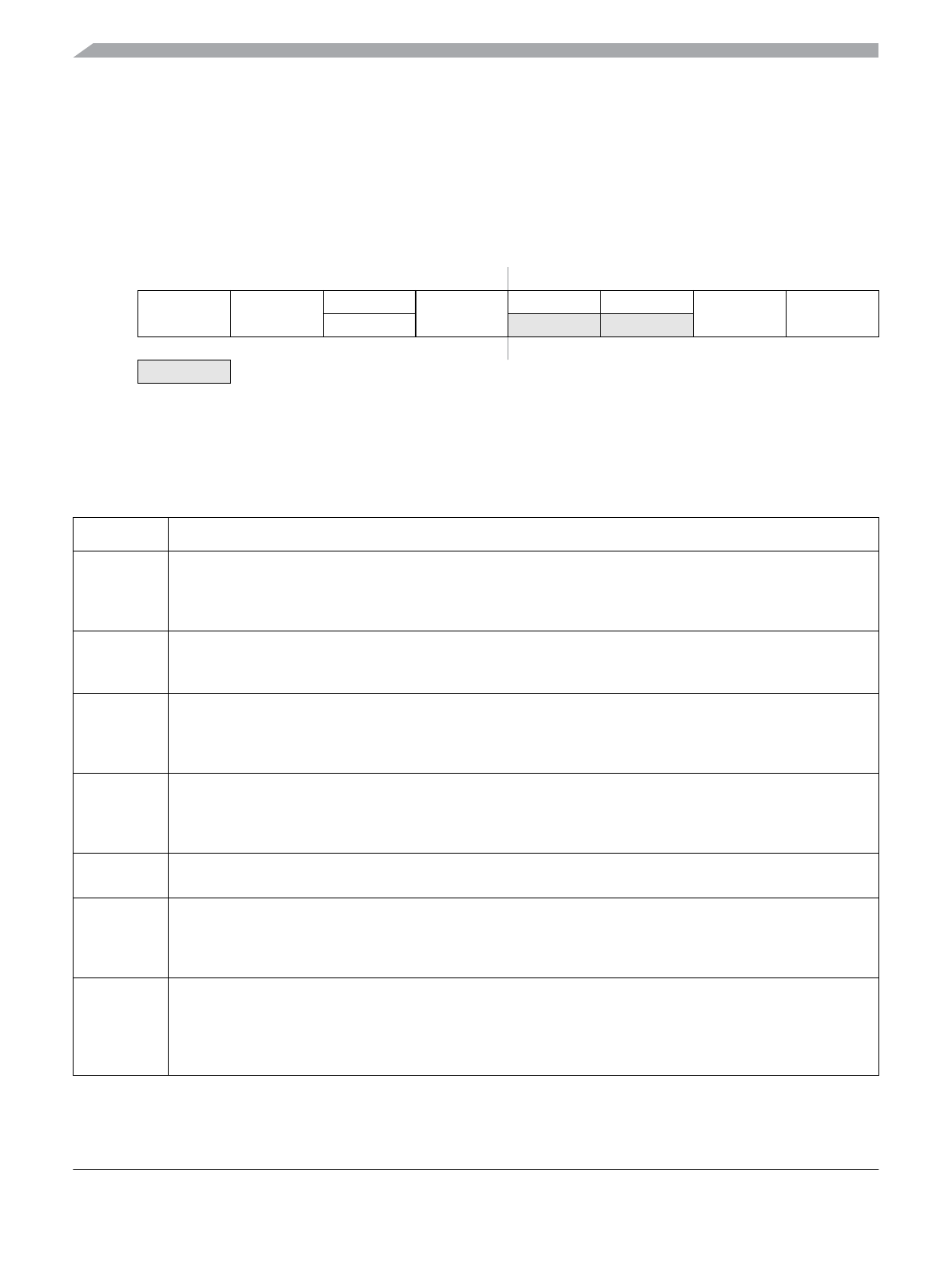

Module Base + 0x0024

76543210

R

PWMIF PWMIE

0

PWMLVL

0 PWM7IN

PWM7INL PWM7ENA

W PWMRSTRT

Reset 00000000

= Unimplemented or Reserved

Figure 12-17. PWM Shutdown Register (PWMSDN)

Table 12-9. PWMSDN Field Descriptions

Field Description

7

PWMIF

PWM Interrupt Flag — Any change from passive to asserted (active) state or from active to passive state will

be flagged by setting the PWMIF flag = 1. The flag is cleared by writing a logic 1 to it. Writing a 0 has no effect.

0 No change on PWM7IN input.

1 Change on PWM7IN input

6

PWMIE

PWM Interrupt Enable — If interrupt is enabled an interrupt to the CPU is asserted.

0 PWM interrupt is disabled.

1 PWM interrupt is enabled.

5

PWMRSTRT

PWM Restart — The PWM can only be restartedif the PWM channel input 7 is de-asserted. After writing a logic

1 to the PWMRSTRT bit (trigger event) the PWM channels start running after the corresponding counter passes

next “counter == 0” phase. Also, if the PWM7ENA bit is reset to 0, the PWM do not start before the counter

passes $00. The bit is always read as “0”.

4

PWMLVL

PWM Shutdown Output Level If active level as defined by the PWM7IN input, gets asserted all enabled PWM

channels are immediately driven to the level defined by PWMLVL.

0 PWM outputs are forced to 0

1 Outputs are forced to 1.

2

PWM7IN

PWM Channel 7 Input Status — This reflects the current status of the PWM7 pin.

1

PWM7INL

PWM Shutdown Active Input Level for Channel 7 — If the emergency shutdown feature is enabled

(PWM7ENA = 1), this bit determines the active level of the PWM7channel.

0 Active level is low

1 Active level is high

0

PWM7ENA

PWM Emergency Shutdown Enable — If this bit is logic 1, the pin associated with channel 7 is forced to input

and the emergency shutdown feature is enabled. All the other bits in this register are meaningful only if

PWM7ENA = 1.

0 PWM emergency feature disabled.

1 PWM emergency feature is enabled.