Chapter 20 Debug (S12XDBGV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

824 Freescale Semiconductor

This describes the format of the information byte used only when tracing from CPU or XGATE in detail

mode. When tracing from the CPU in detail mode, information is stored to the trace buffer on all cycles

except opcode fetch and free cycles. The XGATE entry stored on the same line is a snapshot of the

XGATE program counter. In this case the CSZ and CRW bits indicate the type of access being made by

the CPU, while the XACK and XOCF bits indicate if the simultaneous XGATE cycle is a free cycle (no

bus acknowledge) or opcode fetch cycle. Similarly when tracing from the XGATE in detail mode,

information is stored to the trace buffer on all cycles except opcode fetch and free cycles. The CPU entry

stored on the same line is a snapshot of the CPU program counter. In this case the XSZ and XRW bits

indicate the type of access being made by the XGATE, while the CFREE and COCF bits indicate if the

simultaneous CPU cycle is a free cycle or opcode fetch cycle.

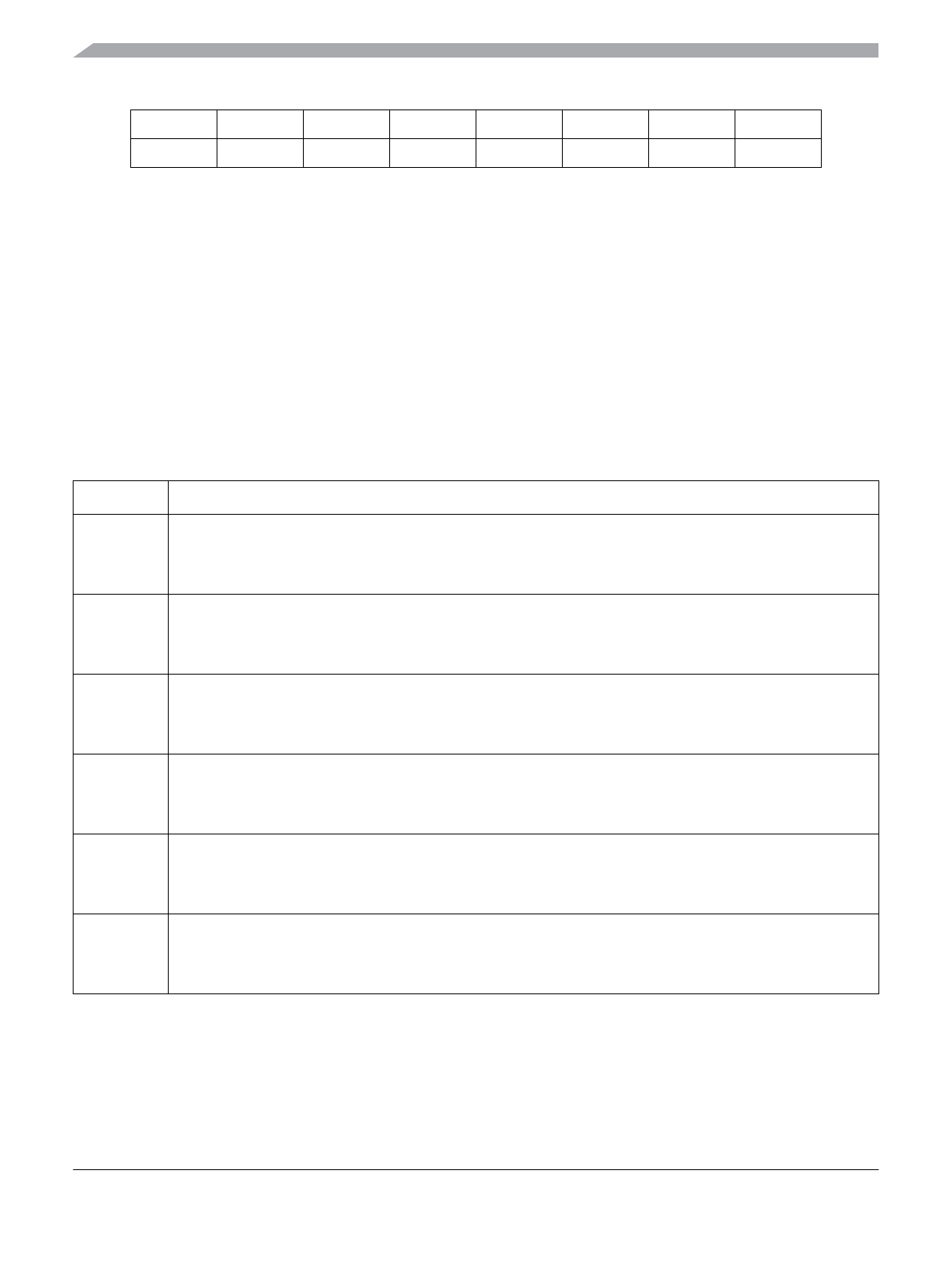

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

CFREE CSZ CRW COCF XACK XSZ XRW XOCF

Figure 20-26. Information Byte CXINF

Table 20-42. CXINF Field Descriptions

Field Description

7

CREE

CPU Free Cycle Indicator — This bit indicates if the stored CPU address corresponds to a free cycle. This bit

only contains valid information when tracing the XGATE accesses in detail mode.

0 Stored information corresponds to free cycle

1 Stored information does not correspond to free cycle

6

CSZ

Access Type Indicator — This bit indicates if the access was a byte or word size access.This bit only contains

valid information when tracing CPU activity in detail mode.

0 Word Access

1 Byte Access

5

CRW

Read Write Indicator — This bit indicates if the corresponding stored address corresponds to a read or write

access. This bit only contains valid information when tracing CPU activity in detail mode.

0 Write Access

1 Read Access

4

COCF

CPU Opcode Fetch Indicator — This bit indicates if the stored address corresponds to an opcode fetch cycle.

This bit only contains valid information when tracing the XGATE accesses in detail mode.

0 Stored information does not correspond to opcode fetch cycle

1 Stored information corresponds to opcode fetch cycle

3

XACK

XGATE Access Indicator — This bit indicates if the stored XGATE address corresponds to a free cycle. This

bit only contains valid information when tracing the CPU accesses in detail mode.

0 Stored information corresponds to free cycle

1 Stored information does not correspond to free cycle

2

XSZ

Access Type Indicator — This bit indicates if the access was a byte or word size access. This bit only contains

valid information when tracing XGATE activity in detail mode.

0 Word Access

1 Byte Access