Chapter 13 Inter-Integrated Circuit (MC9S12XDP512) Block Description

MC9S12XDP512 Data Sheet, Rev. 2.11

Freescale Semiconductor 611

13.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold

the SCL low after completion of one byte transfer (9 bits). In such case, it halts the bus clock and forces

the master clock into wait states until the slave releases the SCL line.

13.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After

the master has driven SCL low the slave can drive SCL low for the required period and then release it.If

the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low

period is stretched.

13.4.2 Operation in Run Mode

This is the basic mode of operation.

13.4.3 Operation in Wait Mode

IIC operation in wait mode can be configured. Depending on the state of internal bits, the IIC can operate

normally when the CPU is in wait mode or the IIC clock generation can be turned off and the IIC module

enters a power conservation state during wait mode. In the later case, any transmission or reception in

progress stops at wait mode entry.

13.4.4 Operation in Stop Mode

The IIC is inactive in stop mode for reduced power consumption. The STOP instruction does not affect IIC

register states.

13.5 Resets

The reset state of each individual bit is listed in Section 13.3, “Memory Map and Register Definition,”

which details the registers and their bit-fields.

13.6 Interrupts

MC9S12XDP512 uses only one interrupt vector.

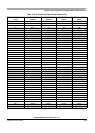

Table 13-9. Interrupt Summary

Internally there are three types of interrupts in IIC. The interrupt service routine can determine the interrupt

type by reading the status register.

Interrupt Offset Vector Priority Source Description

IIC

Interrupt

— — — IBAL, TCF, IAAS

bits in IBSR

register

When either of IBAL, TCF or IAAS bits is set

may cause an interrupt based on arbitration

lost, transfer complete or address detect

conditions