Chapter 22 External Bus Interface (S12XEBIV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

870 Freescale Semiconductor

The following terminology is used:

‘addr’ — value(ADDRx); small letters denote the logic values at the respective pins

‘x’ — Undefined output pin values

‘z’ — Tristate pins

‘?’ — Dependent on previous access (read or write); IVDx: ‘ivd’ or ‘x’; DATAx: ‘data’ or ‘z’

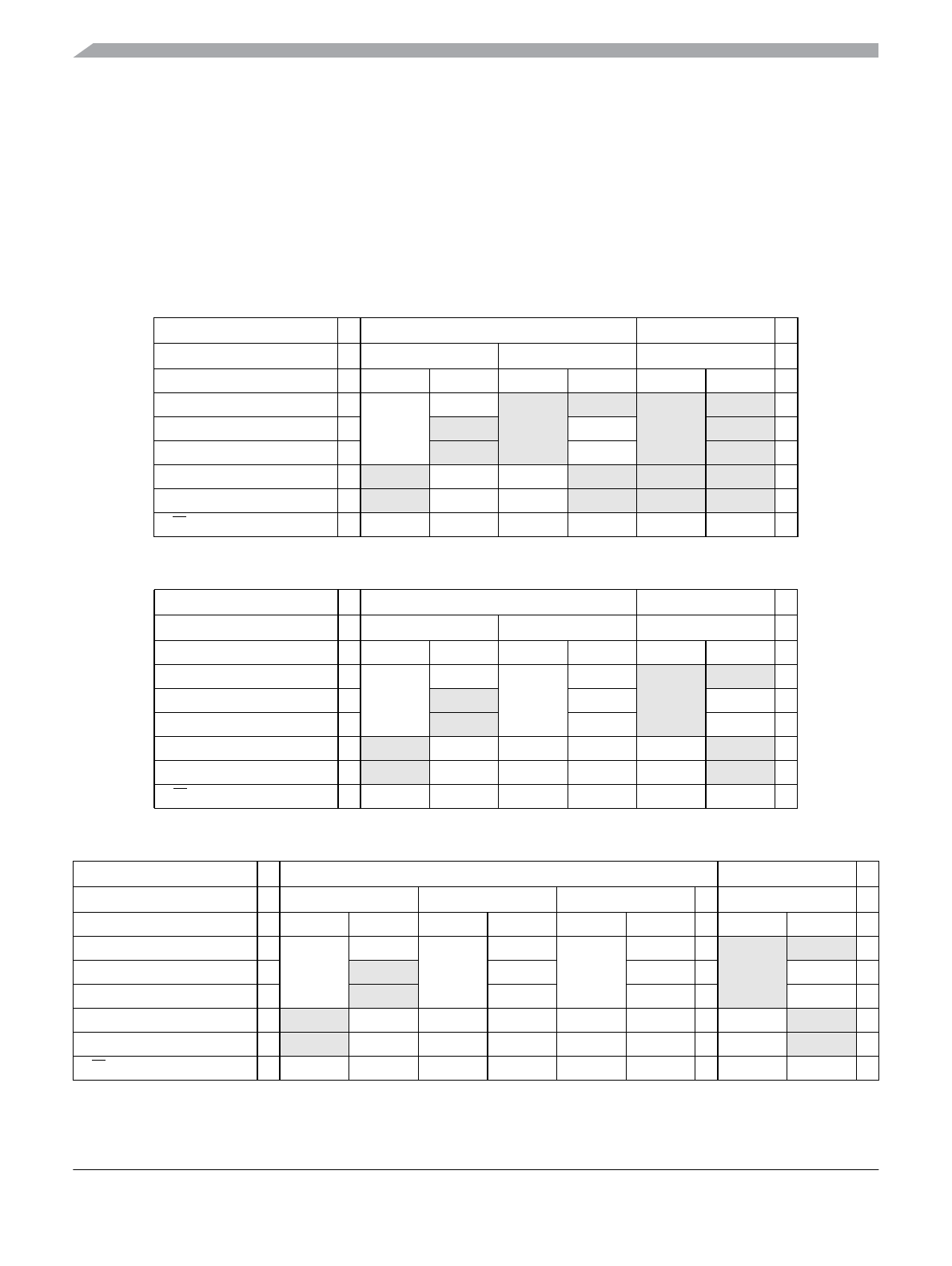

22.4.2.2.1 Read Access Timing

Table 22-9. Read Access (1 Cycle)

Access #0 Access #1

Bus cycle ->

...

123

...

ECLK phase ... high low high low high low ...

ADDR[22:20] / ACC[2:0] ...

addr 0

acc 0

addr 1

acc 1

addr 2

acc 2 ...

ADDR[19:16] / IQSTAT[3:0] ...

iqstat -1 iqstat 0 iqstat 1 ...

ADDR[15:0] / IVD[15:0] ...

? ivd 0 ivd 1 ...

DATA[15:0] (internal read) ...

? zzz z z ...

DATA[15:0] (external read) ...

? z data 0 z data 1 z ...

R/

W ...111111...

Table 22-10. Read Access (2 Cycles)

Access #0 Access #1

Bus cycle ->

...

123

...

ECLK phase ... high low high low high low ...

ADDR[22:20] / ACC[2:0] ...

addr 0

acc 0

addr 0

000

addr 1

acc 1 ...

ADDR[19:16] / IQSTAT[3:0] ...

iqstat-1 iqstat 0 0000 ...

ADDR[15:0] / IVD[15:0] ...

? x ivd 0 ...

DATA[15:0] (internal read) ...

? zzzzz ...

DATA[15:0] (external read) ...

? z z z data 0 z ...

R/

W ...111111...

Table 22-11. Read Access (n–1 Cycles)

Access #0 Access #1

Bus cycle ->

...

123

...

n

...

ECLK phase ... high low high low high low ... high low ...

ADDR[22:20] / ACC[2:0] ...

addr 0

acc 0

addr 0

000

addr 0

000 ...

addr 1

acc 1 ...

ADDR[19:16] / IQSTAT[3:0] ...

iqstat-1 iqstat 0 0000 ... 0000 ...

ADDR[15:0] / IVD[15:0] ...

? xx... ivd 0 ...

DATA[15:0] (internal read) ...

? zzzzz... z z ...

DATA[15:0] (external read) ...

? zzzzz... data 0 z ...

R/

W ...111111...11...