Chapter 23 Memory Mapping Control (S12XMMCV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

890 Freescale Semiconductor

23.3.2.4 Direct Page Register (DIRECT)

Read: Anytime

Write: anytime in special modes, one time only in other modes.

This register determines the position of the direct page within the memory map.

CAUTION

XGATE write access to this register during an CPU access which makes use

of this register could lead to unexpected results.

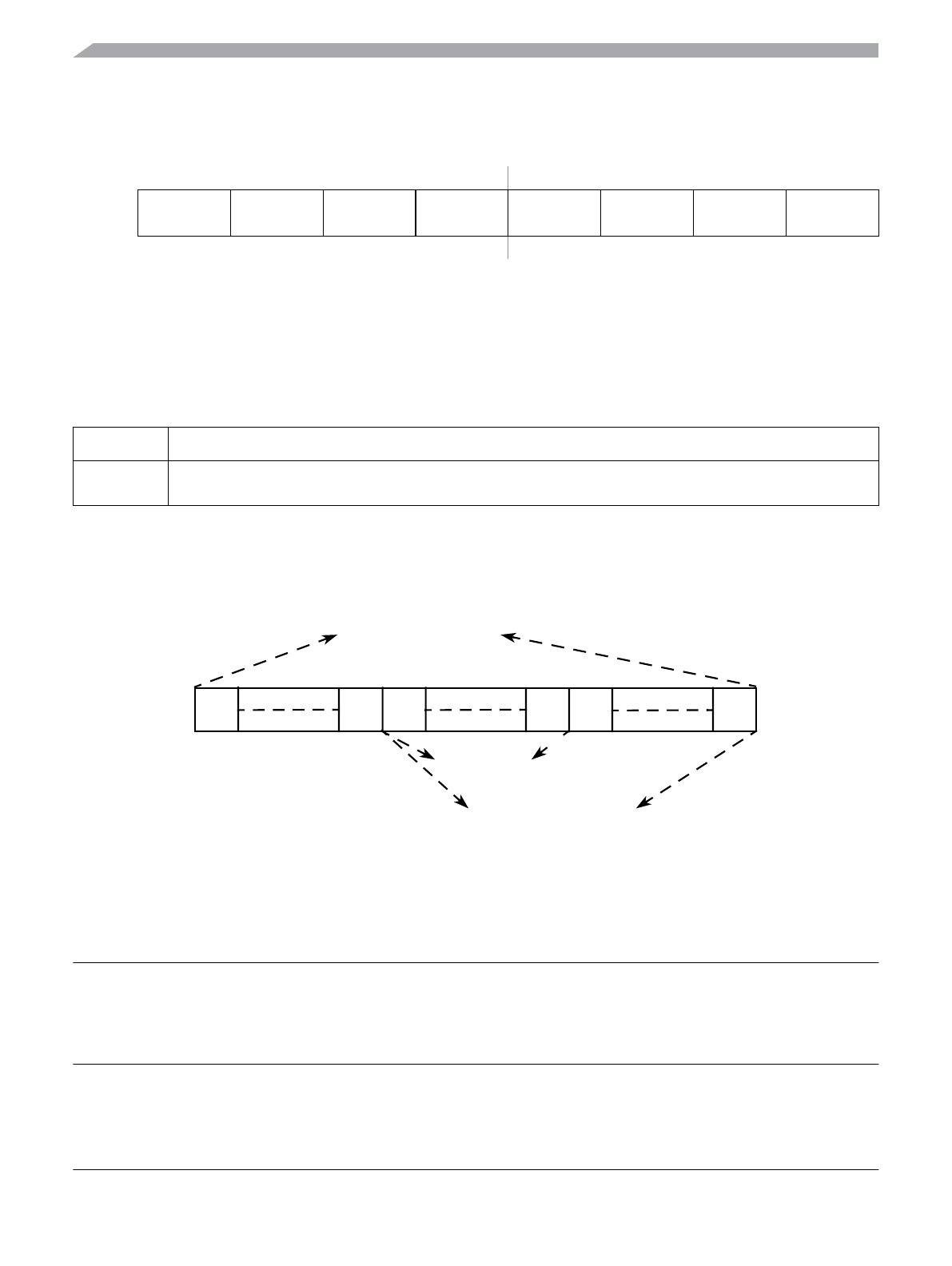

Figure 23-9. DIRECT Address Mapping

Bits [22:16] of the global address will be formed by the GPAGE[6:0] bits in case the CPU executes a global

instruction in direct addressing mode or by the appropriate local address to the global address expansion

(refer to Expansion of the CPU Local Address Map).

Example 23-2. This example demonstrates usage of the Direct Addressing Mode by a global instruction

LDAADR EQU $0000 ;Initialize LDADDR with the value of $0000

MOVB #$80,DIRECT ;Initialize DIRECT register with the value of $80

MOVB #$14,GPAGE ;Initialize GPAGE register with the value of $14

GLDAA <LDAADR ;Load Accu A from the global address $14_8000

Address: 0x0011

76543210

R

DP15 DP14 DP13 DP12 DP11 DP10 DP9 DP8

W

Reset 00000000

Figure 23-8. Direct Register (DIRECT)

Table 23-8. DIRECT Field Descriptions

Field Description

7–0

DP[15:8]

Direct Page Index Bits 15–8 — These bits are used by the CPU when performing accesses using the direct

addressing mode. The bits from this register form bits [15:8] of the address (see Figure 1-9).

Bit15

Bit0

Bit7

Bit22

CPU Address [15:0]

Global Address [22:0]

Bit8

Bit16

DP [15:8]