Chapter 22 External Bus Interface (S12XEBIV2)

MC9S12XDP512 Data Sheet, Rev. 2.11

Freescale Semiconductor 867

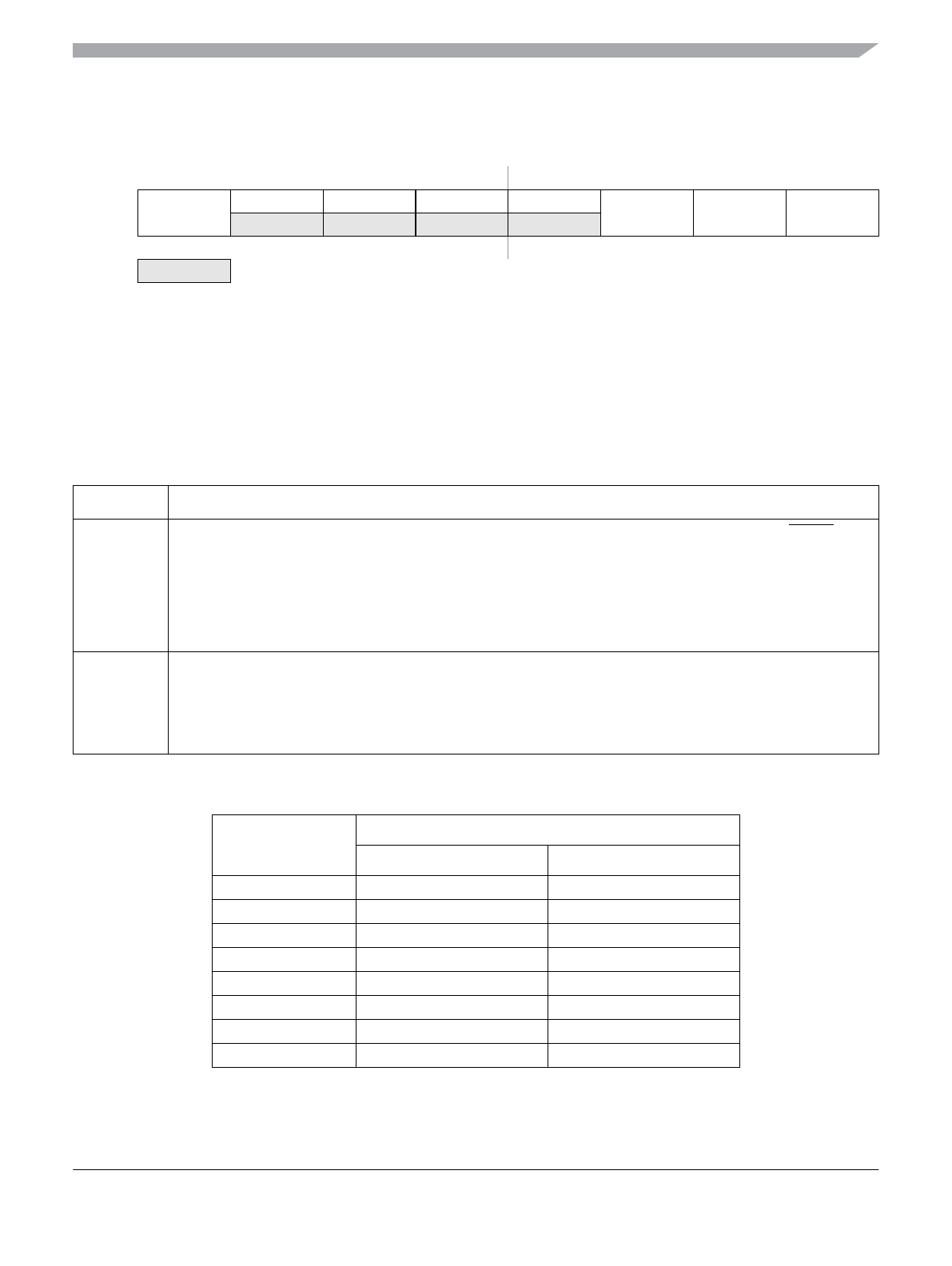

22.3.2.2 External Bus Interface Control Register 1 (EBICTL1)

Read: Anytime. In emulation modes, read operations will return the data from the external bus, in all other

modes the data are read from this register.

Write: Anytime. In emulation modes, write operations will also be directed to the external bus.

This register is used to configure the external access stretch (wait) function.

Module Base +0x000F (PRR)

76543210

R

EWAITE

0000

EXSTR2 EXSTR1 EXSTR0

W

Reset 00000111

= Unimplemented or Reserved

Figure 22-4. External Bus Interface Control Register 1 (EBICTL1)

Table 22-5. EBICTL1 Field Descriptions

Field Description

7

EWAITE

External Wait Enable — This bit enables the external access stretch function using the external

EWAIT input

pin. Enabling this feature may have effect on the minimum number of additional stretch cycles (refer to

Table 22-6).

External wait feature is only activeif enabled in normal expanded mode and emulation expanded mode; function

not available in all other operating modes.

0 External wait is disabled

1 External wait is enabled

2–0

EXSTR[2:0]

External Access Stretch Bits 2, 1, 0 — This three bit field determines the amount of additional clock stretch

cycles on every access to the external address space as shown in Table 22-6. The minimum number of stretch

cycles depends on the EWAITE setting.

Stretch cycles are added as programmed in normal expanded mode and emulation expanded mode; function

not available in all other operating modes.

Table 22-6. External Access Stretch Bit Definition

EXSTR[2:0]

Number of Stretch Cycles

EWAITE = 0 EWAITE = 1

000 1 cycle >= 2 cycles

001 2 cycles >= 2 cycles

010 3 cycles >= 3 cycles

011 4 cycles >= 4 cycles

100 5 cycles >= 5 cycles

101 6 cycles >= 6 cycles

110 7 cycles >= 7 cycles

111 8 cycles >= 8 cycles