1 - 17

1. SUMMARY

1.5 Bus interface

1.5.1 Configuration register

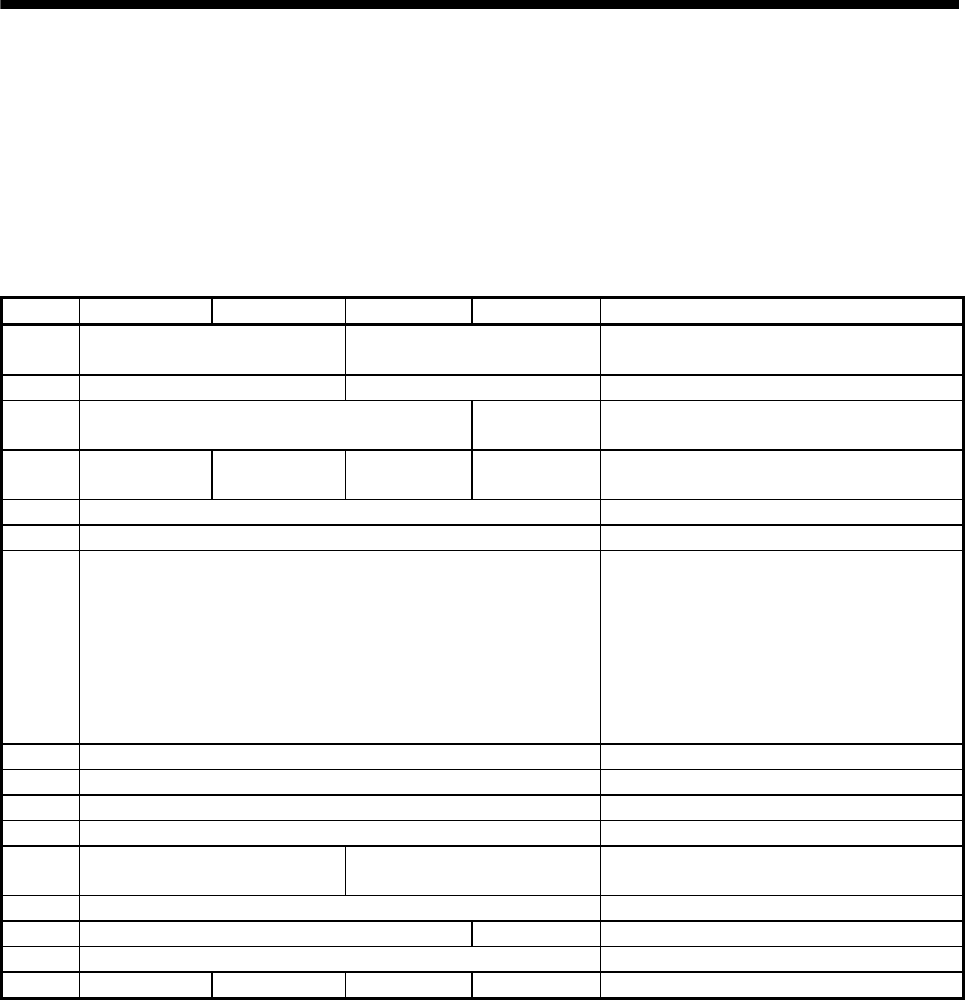

The following shows the configuration register of PCI bus compatible position board (MR-MC210/MR-MC211)

and PCI Express

®

bus compatible position board (MR-MC240/MR-MC241).

(1) PCI bus compatible position board (MR-MC210/MR-MC211)

Address 31 to 24 23 to16 15 to 8 7 to 0 Remarks

00

Device ID

0624

Vendor ID

10BA

Vender ID: Mitsubishi Electric 10BA

Device ID: 0624

04 Status Command

08

Class Code

118000

Revision ID

01

Revision ID: 01

Class Code: 118000 (data processing controller)

0C

BIST

(Note)

Header Type

(Note)

Latency Timer

(Note)

Cache Line Size

(Note)

10 Base Address Register 0

14 Base Address Register 1

18 Base Address Register 2

Dual port memory (including board ID) leading

address

Memory Space Indicator (bit0):

0 (Memory space)

Type (bit1 to 2):

00 (32 bits, arbitrary position of address space)

Prefetchable (bit3):

0 (Prefetch prohibited)

1C Base Address Register 3 (Note)

20 Base Address Register 4 (Note)

24 Base Address Register 5 (Note)

28 Cardbus CIS Pointer (Note)

2C

Subsystem ID

0601

Subsystem Vendor ID

10BA

Subsystem Vender ID: Mitsubishi Electric 10BA

Subsystem ID: 0601

30 Expansion ROM Base Address (Note)

34 (Reserved) (Note) CAP_PTR (Note)

38 (Reserved) (Note)

3C Max_Lat (Note) Min_Gnt (Note) Interrupt Pin 01 Interrupt Line Interrupt Pin: 01(INTA use)

Note. Has not been implemented, therefore, if read an indefinite value will be returned.