SINGLE

COMPONENT

SYSTEM

Unlike

the

8048,

in

the

8022

the

unincremented

program

counter

address

is

stored

in

the

address

stack.

The

stack

contents

are

then

incremented

before

being

loaded

Into

the

program

counter

dur-

ing

a

return

(RET)

from

subroutine.

However,

dur-

ing

a return (RETI) from interrupt, the stack

contents are

loaded

directly into the program

counter.

This

difference

makes

it imperative to

use

only

RETI's

to return

from

interrupts,

and

RET's

to

return

from

subroutines.

Since

the

program

counter's addresses

are

11

bits

long,

two bytes

or

registers

must

be

used

to

store a

single

address.

Thus,

the

16-byte

program

counter

stack

permits

up

to a total of 8

levels

of

subroutine

nesting

without

overflowing

the

stack.

If overflow does occur, the deepest address

stored

(locations

8

and

9)

will

be

overwritten

and

lost

since

the

stack

pointer

overflows

from

111

to

000.

It

also

underflows

from

000 to

111.

If

a

par-

ticular application

does

not

require

8 levels of

nesting,

the

unused

portion

of

the

progam

counter

stack

may

be

used

as

any

other indirectly

addres-

sable

RAM

location.

For

example,

if

only

3

levels

of

subroutine

nesting

are

used,

then

only

locations

8-13

need

be

reserved

for

the

program

counter

stack,

and

locations

14-23

can

be

used

for

data

storage.

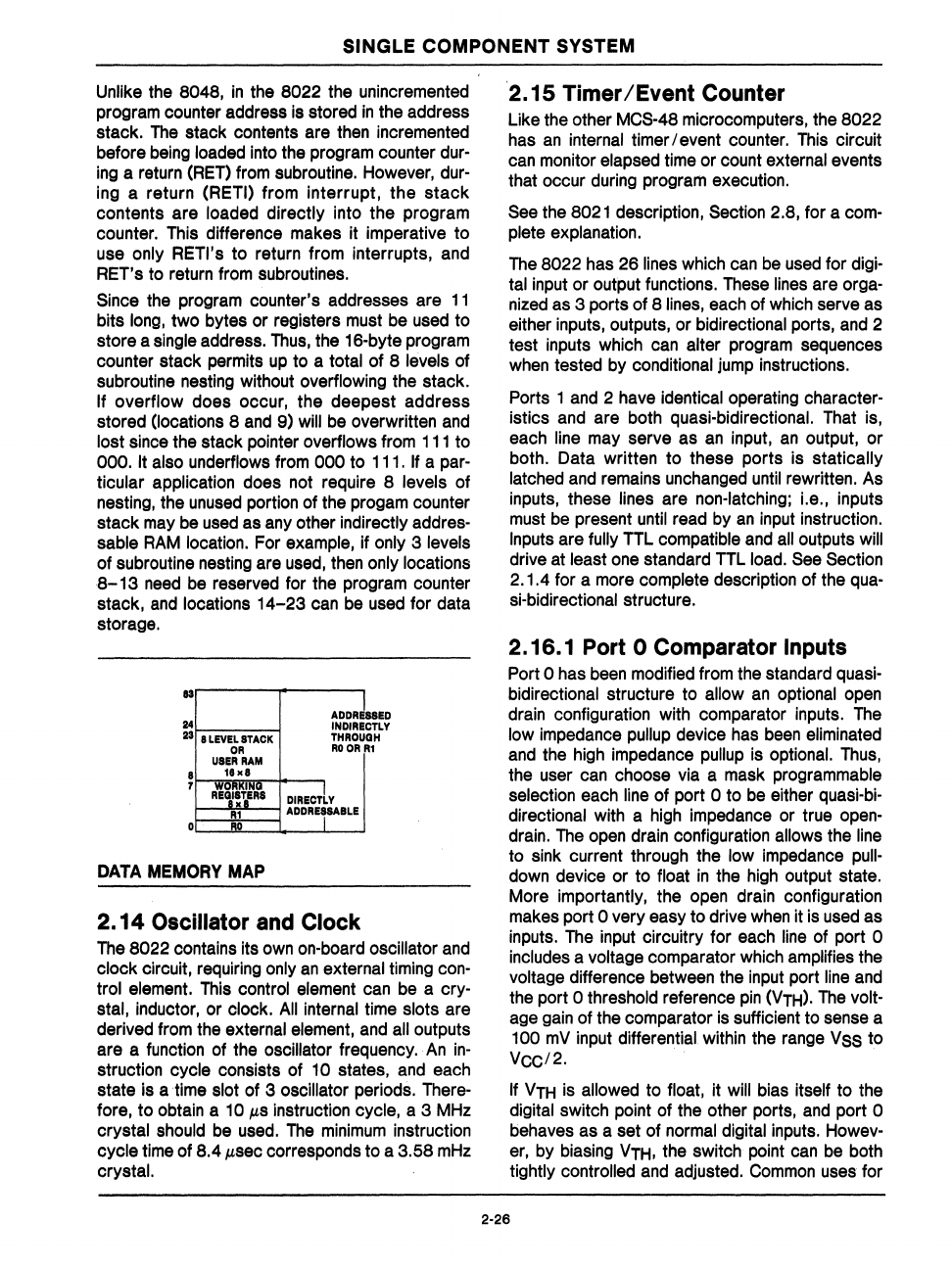

18

24

23

8

LEVEL

aTACK

OR

USER

RAM

18.8

Rl~l\r:.

1

DATA

MEMORY

MAP

ADDRJ.

IN

DIRE

THROU

EIIED

CTLV

QH

RGORR

1

DIRECTlv

ADDR~8LE

2. 14 Oscillator and Clock

The

8022

contains

its

own

on-board

oscillator

and

clock circuit,

requiring

only

an

external

timing

con-

trol

element.

This

control

element

can

be

a cry-

stal,

inductor,

or

clock.

All

Internal

time

slots

are

derived

from

the

external

element,

and

all

outputs

are a

function

of

the

oscillator

frequency.·

An

in-

struction

cycle

consists

of

10

states,

and

each

state

is

a

time

slot

of

3 oscillator

periods.

There-

fore,

to

obtain

a

10

fJ,s

instruction

cycle, a 3

MHz

crystal

should

be

used.

The

minimum

instruction

cycle

time

of

8.4

fJ,sec

corresponds

to a 3.58

mHz

crystal.

'2.15 Timer/Event Counter

Like

the

other

MCS-48

microcomputers,

the

8022

has

an

internal

timer

I

event

counter.

This

circuit

can

monitor

elapsed

time

or

count

external

events

that

occur

during

program

execution.

See

the

8021

description,

Section

2.8,

for a

com-

plete

explanation.

The

8022

has

26

lines

which

can

be

used

for

digi-

tal

input

or

output

functions.

These

lines

are

orga-

nized

as

3 ports of 8

lines,

each

of

which

serve

as

either

inputs,

outputs,

or

bidirectional

ports,

and

2

test

inputs

which

can

alter

program

sequences

when

tested

by

conditional

jump

instructions.

Ports

1

and

2

have

identical

operating

character-

istics

and

are

both

quasi-bidirectional.

That

is,

each

line

may

serve

as

an

input,

an

output,

or

both.

Data

written to these ports

is

statically

latched

and

remains

unchanged

until

rewritten.

As

inputs,

these

lines

are

non-latching;

i.e.,

inputs

must

be

present

until

read

by

an

input

instruction.

Inputs

are

fully

TTL

compatible

and

all

outputs

will

drive

at

least

one

standard

TTL

load.

See

Section

2.1.4 for a

more

complete

description

of

the

qua-

si-bidirectional

structure.

2.16.1 Port 0 Comparator Inputs

Port

0

has

been

modified

from

the

standard

quasi-

bidirectional

structure

to

allow

an

optional

open

drain

configuration

with

comparator

inputs.

The

low

impedance

pullup

device

has

been

eliminated

and

the

high

impedance

pullup

is

optional.

Thus,

the

user

can

choose

via

a

mask

programmable

selection

each

line

of

port a to

be

either

quasi-bi-

directional

with

a

high

impedance

or

true

open-

drain.

The

open

drain

configuration

allows

the

line

to

sink

current

through

the

low

impedance

pull-

down

device

or

to

float

in

the

high

output

state.

More

importantly,

the

open

drain

configuration

makes

port 0

very

easy

to

drive

when

it

is

used

as

inputs.

The

input

circuitry for

each

line

of

port 0

includes

a

voltage

comparator

which

amplifies

the

voltage

difference

between

the

input

port

line

and

the

port 0

threshold

reference

pin

(VTH).

The

volt-

age

gain

of

the

comparator

is

sufficient

to

sense

a

100

mV

input

differential

within

the

range

VSS

to

VCC

/2

.·

.

If

VTH

is

allowed

to

float,

it

will

bias

itself to

the

digital switch

point

of

the

other

ports,

and

port a

behaves

as

a set of

normal

digital

inputs.

Howev-

er,

by

biasing

VTH,

the

switch

point

can

be

both

tightly

controlled

and

adjusted.

Common

uses

for

2·26