8155/8156/8155-2/8156-2

TIMER SECTION

The timer is a 14-bit down-counter that counts the TIMER

IN pulses

and provides either a square wave

or

pulse

when terminal

count

(TC) is reached.

The timer has the

I/O

address XXXXX100forthe low order

byte

of

the register and the

I/O

address

XXXXX101

for

the high order byte

of

the register.

(See

Figure 5).

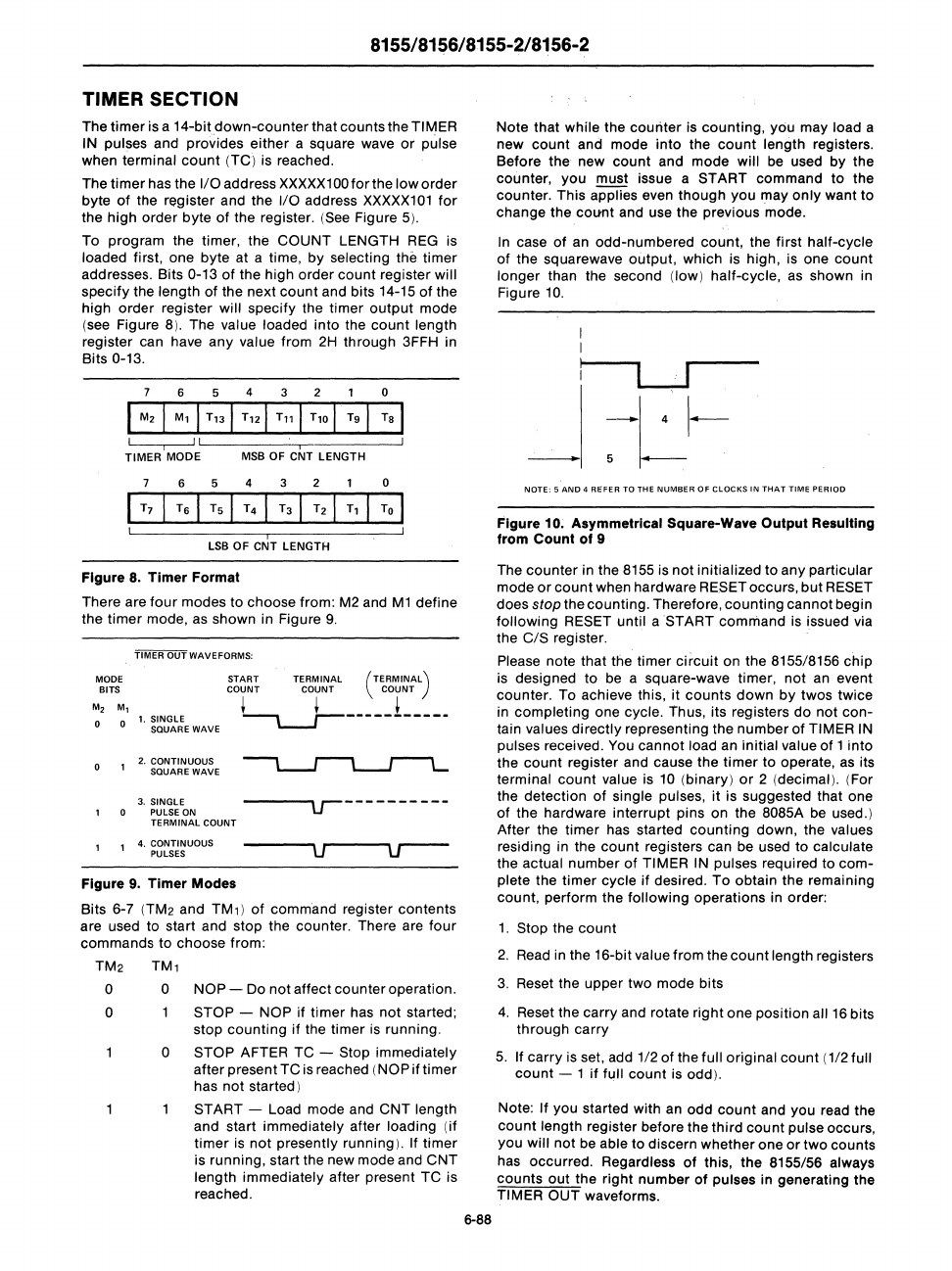

To program the timer,

the COUNT LENGTH

REG

is

loaded first, one byte at a time, by selecting the timer

addresses. Bits 0-13

of

the high order count register will

specify the length of the next count and bits 14-15 of the

high order register

will specify the timer output mode

(see Figure 8). The

value loaded into the count length

register can have any value from

2H

through 3FFH in

Bits 0-13.

6 5

4

3 2

0

I

M21

Ml

I

T131

T121

Tll

I

Tl0

I

T91

Tal

I

I

II

I

I

TIMER MODE

MSB

OF CNT LENGTH

65432

o

I

LSB

OF

CNT LENGTH

Figure

8.

Timer Format

There are

four

modes to choose from: M2 and

M1

define

the timer mode,

as

shown in Figure

9.

MOOE

BITS

M2

M1

o 0

TIMER

OUT

WAVEFORMS:

START

COUNT

TERMINAL

(TERMINAL)

COUNT COUNT

1.

SINGLE

SQUARE

WAVE

2.

CONTINUOUS

SQUARE

WAVE

3.

SINGLE

PULSE ON

TERMINAL

COUNT

4. CONTINUOUS

PULSES

~

_____

1

____

_

---~----------

-------ur------~

Figure 9. Timer Modes

Bits 6-7 (TM2 and TM1) of command register contents

are used to start and stop the counter. There are four

commands to choose from:

TM2

TMl

o 0 NOP - Do not affect counter operation.

o STOP - NOP if timer has not started;

stop counting if the timer is running.

o STOP AFTER TC - Stop immediately

after present TC is reached (NOP

if

timer

has not started)

START - Load mode and

CNT

length

and start immediately after loading (if

timer is not presently running).

If timer

is running, start the new mode and

CNT

length immediately after present TC is

reached.

6-88

Note that while the counter is counting, you may load a

new count and mode into the count

length registers.

Before the new count and mode will be used by the

counter, you must issue a

START command

to

the

counter. This

applies even though you may

only

want to

change the

cOllnt and use the previous mode.

In case

of

an odd-numbered count, the first half-cycle

of the squarewave output, which is high, is one count

longer than the second (low) half-cycle,

as

shown in

Figure

10.

NOTE;

5

AND

4 REFER TO THE

NUMBER

OF

CLOCKS

IN

THAT

TIME PERIOD

Figure 10; Asymmetrical Square-Wave

Output

Resulting

from Count

of

9

The counter in the 8155 is not initialized

to

any particular

mode

or

count when hardware RESET occurs, but RESET

does stop the counting. Therefore, counting cannot begin

following RESET until a START command is issued via

the

CIS register.

Please note that tlie timer circuit on the 8155/8156 chip

is designed to

be

a square-wave timer, not

an

event

counter. To achieve this, it counts

down

by

twos twice

in

completing one cycle. Thus, its registers do not con-

tain

values directly representing the number of TIMER IN

pulses

received. You cannot load

an

initial value of 1 into

the count register and cause the timer to operate,

as

its

terminal count value is

10

(binary)

or

2 (decimal). (For

the detection

of

single pulses,

it

is suggested that one

of

the hardware interrupt pins on the 8085A be used.)

After the timer has started counting down, the

values

residing in the count registers can be used to calculate

the actual number of TIMER IN pulses required to com-

plete the timer cycle if desired.

To

obtain the remaining

count, perform the

following operations in order:

1.

Stop the count

2.

Read in the 16-bit value from the

count

length registers

3.

Reset the upper two mode bits

4.

Reset the carry and rotate right one position all

16

bits

through carry

5.

If carry is set, add 1/2 of the full original count

(112

full

count - 1

if

full count is odd).

Note:

If you started with

an

odd

count

and you read the

count

length register before the

third

count pulse occurs,

you

will not be able

to

discern whether one

or

two counts

has occurred.

Regardless

of

this, the 8155/56 always

counts

out

the right number

of

pulses in generating the

TIMER OUT waveforms.