2716

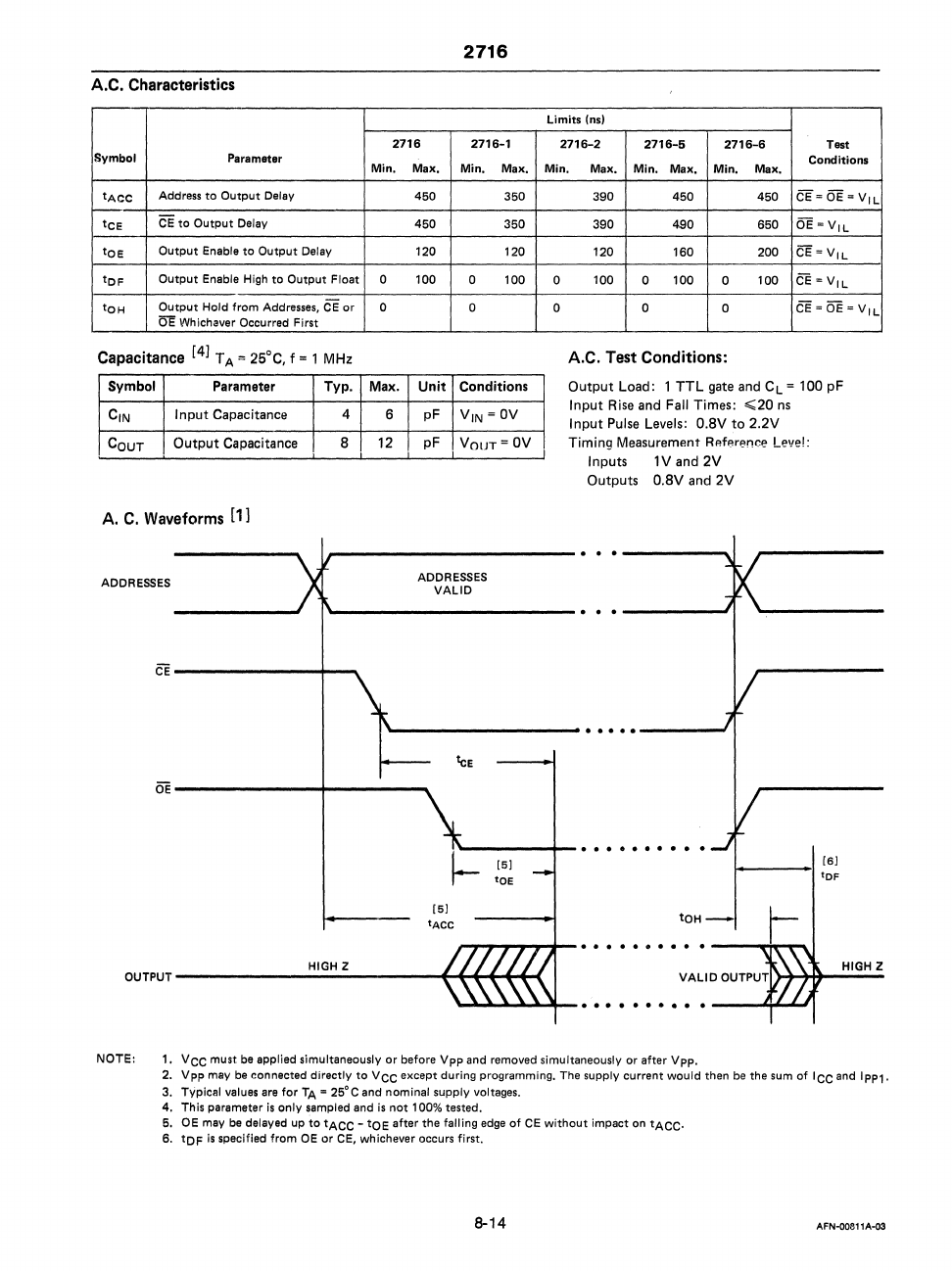

A.C. Characteristics

Limits

(ns)

2716

2716-1

2716-2

2716-5

2716-6

Test

Symbol

Parameter

Conditions

Min.

Max.

Min. Max.

Min.

Max.

Min.

Max.

Min.

Max.

tACC

Address

to

Output

Delay

450

350

390

450

450

CE=OE=VIL

tCE

CE

to

Output

Delay

450

350

390

490

650

OE =

VIL

tOE

Output

Enable

to

Output

Delay

120

120 120

160

200

CE=VIL

tOF

Output

Eneble High

to

Output

Float

0 100

0 100

0

100

0 100

0

100

CE=VIL

tOH

Output

Hold

from

Addresses,

CE

or

0

0

0 0 0

CE

= OE =

VIL

DE

Wh

iehever

Oeeu

rred First

Capacitance

[4]

TA =

2SoC,

f = 1 MHz

A.C. Test Conditions:

Symbol Parameter Typ.

CIN

Input Capacitance 4

Max.

Unit

6

pF

Conditions

VIN

=

OV

Output

Load: 1

TTL

gate

and

CL = 100 pF

Input

Rise

and

Fall Times: ';;;20

ns

COUT

Output

Capacitance 8 12

I I I

A.

C.

Waveforms [1]

ADDRESSES

CE--------------~--~

pF

VOlJT =

OV

I

ADDRESSES

VALID

I

Input

Pulse

Levels: 0.8V

to

2.2V

Timing

Measurement

Rp.fp.renr.e

Leve!:

Inputs 1 V and

2V

Outputs 0.8V and

2V

5E--------------~----------~

1''------+-.

. . . . . . . . .

,...~....,....,,...,,...,t--.

• • • • • •

HIGH Z

OUTPUT----------------------------i-~~_+~<

'-a..

................

't--

•••••••

NOTE:

1. VCC must

be

applied simultaneously

or

before

Vpp

and removed simultaneously

or

after

Vpp.

[6J

'OF

HIGH Z

2.

Vpp

may

be

connected

directly

to

VCC except during programming. The supply

current

would

then

be

the sum

of

ICC and IpP1.

3. Typical values

are

for

TA

=

25'

C and nominal supply voltages.

4. This parameter

is

only

sampled and

is

not

100% tested.

5.

OE may

be

delayed up

to

tACC

- tOE

after

the falling

edge

of

CE

without

impact on

tACC.

6.

tDF

is

specified

from

OE

or

CE,

whichever occurs first.

8-14

AFN-00811

A-03