8205

Logic Element Example

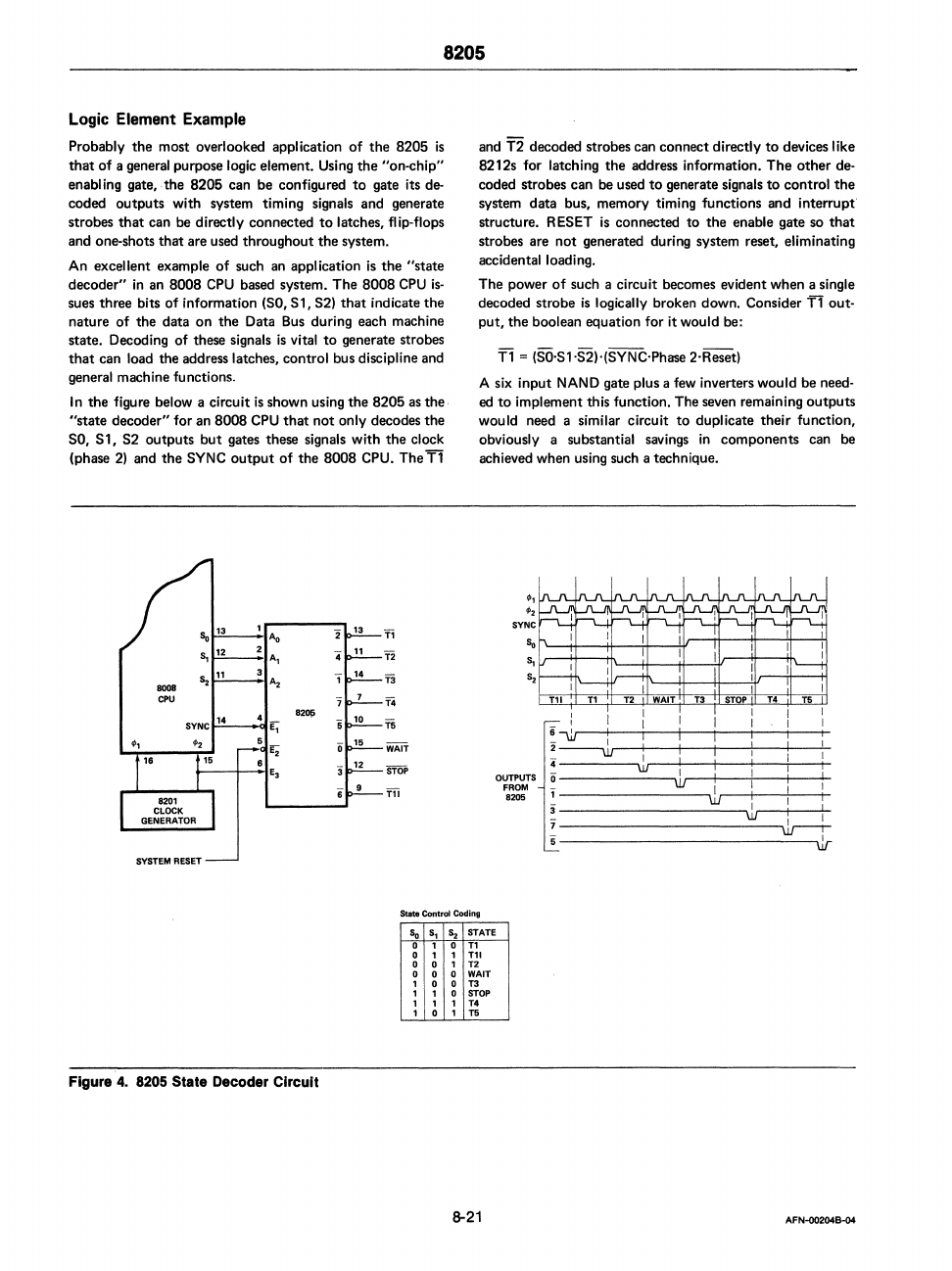

Probably the most overlooked application of the 8205

is

that of a general purpose logic element.

Using

the "on-chip"

enabling gate, the 8205 can be configured

to

gate its

de-

coded outputs with system timing signals and generate

strobes

that

can

be

directly connected

to

latches, flip-flops

and one-shots that are

used

throughout the system.

An

excellent example of such

an

application

is

the "state

decoder"

in

an

8008

CPU

based system. The 8008

CPU

is-

sues three bits of information

(SO,

S1, S2)

that

indicate the

nature of the data on the Data

Bus

during each machine

state. Decoding of these signals

is

vital

to

generate strobes

that

can load the address latches, control bus discipline and

general machine functions.

In

the figure below a circuit

is

shown using the 8205

as

the

"state decoder" for

an

8008

CPU

that not only decodes the

SO,

S1,

S2

outputs but gates these signals with the clock

(phase

2)

and the

SYNC

output of the 8008

CPU.

The

T1

2

'3

1'1

..

11

1'2

-,

"

T3

7

1'4

82O!)

10

..

TO

0

10

WAIT

12

STOP

E,

3"

.-

ru

SYSTEM

RESET

and T2 decoded strobes can connect directly

to

devices like

8212s for latching

the

address information. The other de-

coded strobes can

be

used

to

generate signals to control

the

system data bus, memory timing functions and interrupt

structure. RESET

is

connected to the enable gate so that

strobes are not generated during system reset, eliminating

accidental loading.

The power of such a circuit becomes evident when a single

decoded strobe

is

logically broken down. Consider

fi

out-

put, the boolean equation for it would be:

T1

~

(SO'S1'S2)-(SYNC'Phase 2'Reset)

A

six

input

NAND

gate plus a

few

inverters would be need-

ed

to

implement this function. The seven remaining outputs

would need a similar circuit

to

duplicate their function,

obviously a substantial savings

in

components can

be

achieved when using such a technique .

. ,

.,

So

S,

I

I

I

T1I

T1

T2

WAIT

T3

STOP

T'

TO

I

I

I

I

I I

Sill

I

I

I

I

I

- I

I

I

I

I

2-..u

I

1

I

..

ill

I

I

I

I

OUTPUTS

0

I

I

I

I

FROM

ill

I

I

I

,-

I

8200

W I

I

I

I

7

W

I I

..

w---r

Iff

State

Control

Coding

So

.,

"

STATE

0

1

0

T1

0 1 1

T1I

0 0

1

T2

0

0

0

WAIT

1 0 0

T3

1

1

0

STOP

1

1

1

T'

1 0 1 T5

Figure

4.

8205 State Decoder Circuit

8-21

AFN-002048-04