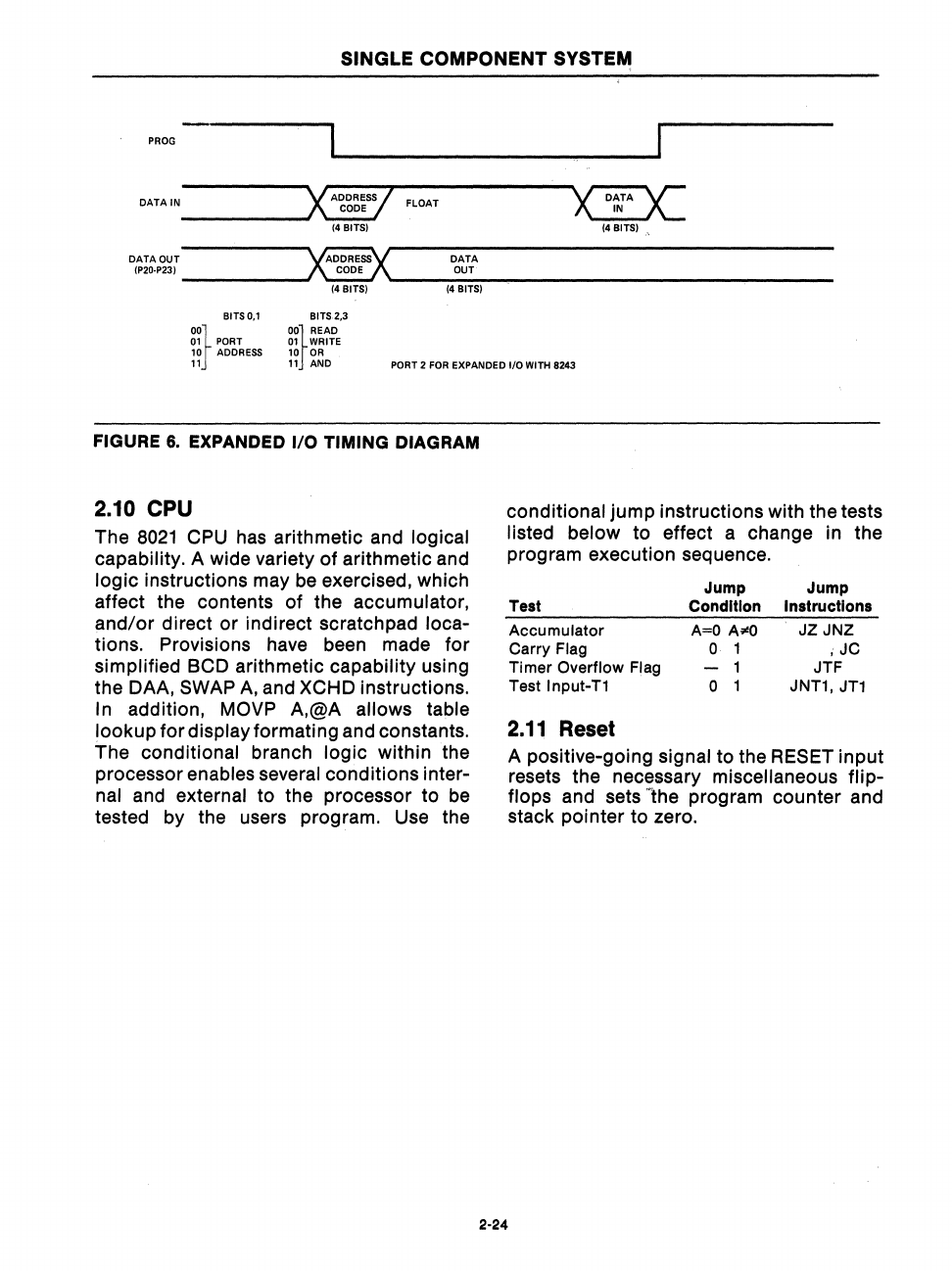

SINGLE COMPONENT SYSTEM

PROG

)Cf)C

(4

BITS)

V

ADDRESSJ

FLOAT

~

------

14

BITS)

DATA

IN

DATA

OUT

~

DATA

(P20·P23)

~

OUT

-----....

(4

BITS)

'---~(4~BIT=S)~---------------

BITS

0,1

01

PORT

10

OR

OO}

10

ADDRESS

11

BITS

2,3

OO}READ

01

WRITE

11

AND

PORT

2

FOR

EXPANDED

1/0

WITH

8243

FIGURE

6.

EXPANDED I/O TIMING DIAGRAM

2.10

CPU

The

8021

CPU has arithmetic and logical

capability.

A wide variety

of

arithmetic and

logic instructions may

be

exercised, which

affect the contents of the

accumulator,

and/or

direct or indirect scratch pad loca-

tions. Provisions have been made for

simplified BCD arithmetic capability using

the DAA,

SWAP

A,

and XCHD instructions.

In addition, MOVP A,@A allows table

lookup

for display formating and constants.

The

conditional branch logic within the

processor

enables several conditions inter-

nal and external to the processor to

be

tested by the users program. Use the

conditional jump instructions with the tests

listed below to effect a change in the

program execution sequence.

2-24

Test

Accumulator

Carry Flag

Timer Overflow Flag

Test

Input-T1

2.11

Reset

Jump

Condition

A=O

A"'O

o 1

1

o 1

Jump

Instructions

JZ JNZ

,JC

JTF

JNT1,

JT1

A positive-going signal to the RESET input

resets the necessary

miscellaneous flip-

flops

and sets "the program counter and

stack

pOinter to zero.