+5V

GNo

b26

L

Vee

VOD

Vss

2

-

XTAL

1

3

-

XTAl2

4

-

RESET

8049

7

-

EA

8048

8748

8021"

-ss

8035

8039

8022·

1

_TO

39

Tl

6

-

iNT

ADDING 16 INPUT LINES

+5V

GNo

b26

L

Vee

VOD

Vss

2

-

XTAlT

3

-

XTAl2

4

-

RESET

7

-

EA

8049

8048

ss

8748

1

-TO

39

-Tl

6

-

iNf

APPLICATION EXAMPLES

PlO 27

Pl1

28

P12 29

PT3

30

.14

31

P15

32

PT6

33

.17

34

P20 21

P21

22

P22

23

P23

24

P24 35

P25

36

P26

37

P27

38

~-+---IA

17:--+---1

C

~-+='-----Io

DBO

12

DBT

13

DB2'4

DB3 15

DB4 16

DBS

11

DBB 18

W

EO

74150

(24)

El

E2

E3

E4

E5

E6

E7

E8

E9

El0

Ell

E12

E13

E14

E15

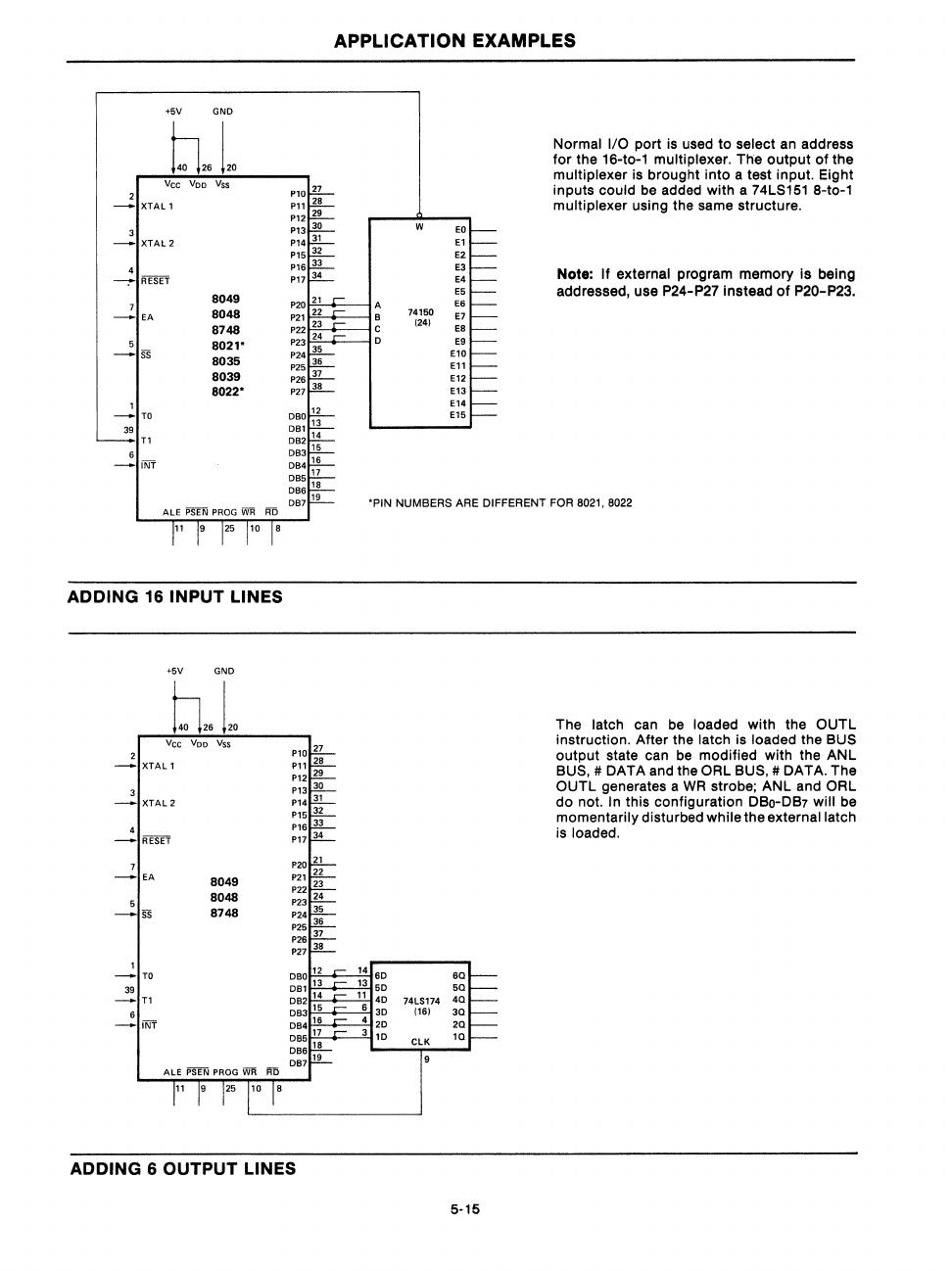

Normal 1/0 port is used

to

select an address

for the 16-to-1

multiplexer. The output

of

the

multiplexer is brought into a test input. Eight

inputs

could

be

added with a

74LS151

8-to-1

multiplexer using the same structure.

Nota:

If

external program memory Is being

addressed, use P24-P27 instead

of

P20-P23.

DB7

19

'PIN

NUMBERS ARE DIFFERENT FOR 8021. 8022

PTO

27

Pl1

28

P12

29

PT3

30

P14

31

P15

32

P16

33

P17

34

PlO

21

P21

22

P22

23

.23

24

P24

35

P25

36

P26

37

P27

38

DBD

12

14

60

DBT

13

13

60

oB2 14

11

40

0B3 15

6

3D

oB4

16

20

DBS

17

10

DBB

18

DB7

19

74LS174

(16)

ClK

6a

sa

4a

3a

2a

la

The latch can

be

loaded with the OUTL

instruction. After the latch is loaded the BUS

output state can

be

modified with the ANL

BUS, # DATA and the ORL BUS, # DATA. The

OUTL generates a

WR

strobe; ANL and ORL

do not. In this configuration DBo-DB7 will

be

momentarily disturbed while the external latch

is loaded.

ADDING 6 OUTPUT LINES

5·15