8251

A/S2657

PROGRAMMABLE COMMUNICATION INTERFACE

• Synchronous and Asynchronous

Operation

• Synchronous

5·8

Bit Characters;

Internal or External Character Synchro·

nization; Automatic Sync Insertion

•

Asynchronous 5·8 Bit Characters;

Clock

Rate-1,

16 or 64 Times Baud

Rate; Break Character Generation;

1,

1

Y2,

or 2 Stop Bits; False Start Bit

Detection; Automatic Break Detect

and Handling.

•

Synchronous Baud Rate -

DC

to 64K

Baud

• Asynchronous Baud Rate - DC to

19.2K Baud

• Full Duplex, Double Buffered, Trans·

mitter and Receiver

• Error Detection - Parity, Overrun and

Framing

• Ful!y Compatible with 808018085 CPU

•

28·Pin DIP Package

• All Inputs and Outputs are TTL

Compatible

• Single + 5V Supply

• Single

iTL

Clock

The

Intel'" 8251A is the enhanced version

of

the industry standard, Intel'"

8251

Universal Synchronous/Asynchronous

Receiver/Transmitter

(USART),

designed for data communications with Intel's new high performance family

of

microprocessors such

as

the

8085.

The 8251A is used

as

a peripheral device and is programmed by the

CPU

to operate

using virtually any serial data transmission technique presently in use (including

IBM "bi-sync"). The USART accepts

data characters from the

CPU

in parallel format

and

then converts them into a continuous serial data stream for

transmission.

Simultaneously,

it

can receive serial data streams and convert them into parallel data characters for the

CPU.

The

USART

will signal the

CPU

whenever

it

can accept a new character for transmission or whenever

it

has

received a character for the

CPU.

The

CPU

can read the complete status

of

the

USART

at any time. These include data

transmission errors and control signals such

as

SYNDET, TxEMPTY. The chip is constructed using N·channel silicon

gate technology.

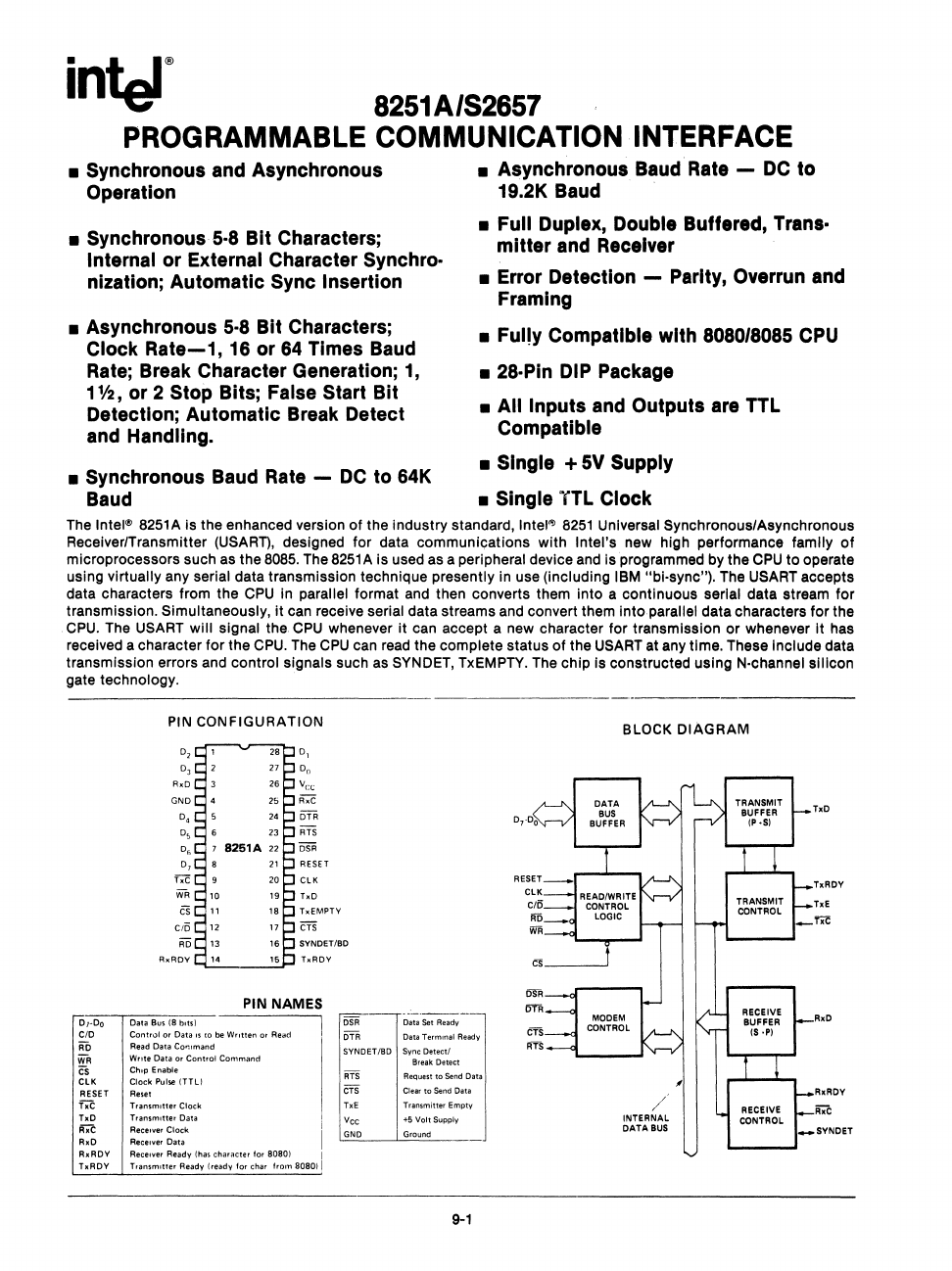

PIN

CONFIGURATION

BLOCK

DIAGRAM

D,

D,

D]

D"

R,D

v

cc

.:

GND

R.e

D,

DTR

°

7

,0

0

Ds

RTS

D"

DSR

D,

RESET

r;c

eLK

ViR

hD

cs

TlCEMPTY

CIO

eTS

AD

SYNDn/BO

RIIRDV

TlCRDY

PIN

NAMES

----.~----

0,-00

Data Bus (8

blts~

I

DSR

Data Set Ready

e/D

Control

or Data

15

to

be

Wntten

Of

Re<ld

DTR

Data Terminal Ready

AD

Read

Data

CO'1lmand

SYNDET/SD

Sync Detectl

ViR

Write Data or Control

Command

Break Detect

Os

Chip

Enable

RTS

Request

to

Send Data

eLK

Clock

Pulse

ITTlI

RESET

Reset

CTS

Clear

to

Send Data

fKC

Transm!t1er

Clock

T.E

Transmitter

Empty

T.D

Transmitter Data

Vee

+5

Volt

Supply

R;c

Receiver Clock

I

GND

Ground

R.D

Receiver Data

RxRDY

Receiver Ready Ihas character for 80801

I

hRDY

Transmitter Ready Iready for char

from

808011

9-1