8259A

INTERRUPT

REQUEST

REGISTER

(IRR)

AND

IN·SERVICE

REGISTER

(ISR)

The interrupts at the

IR

input lines are handled

by

two

registers

in

cascade, the Interrupt Request Register

(IRR)

and the In·Service Register

(ISR).

The

IRR

is used

to

store all the interrupt leveis which are requesting ser·

vice; and the

ISR

is used

to

store all the interrupt levels

which are being serviced.

PRIORITY

RESOLVER

This logic block determines the priorities of the bits set

in the

IRR.

The highest priority is selected and strobed

into the corresponding bit of the

ISR

during INTA pulse.

INTERRUPT

MASK

REGISTER

(IMR)

The IMR stores the bits which mask the interrupt lines

to

be

masked.

The

IMR

operates on the

IRR.

Masking of

a higher priority input will not affect the interrupt

request lines of lower priority.

INT

(INTERRUPT)

This output goes directly to the

CPU

interrupt input. The

V

OH

level

on

this line is designed to

be

fully compatible

with the

8080A,

8085A

and

8086

input levels.

iNTi

(INTERRUPT

ACKNOWLEDGE)

INTA pulses will cause the

8259A

to release vectoring

information onto the data bus.

The

format of this data

• depends

on

the system mode ("PM)

of

the

8259A.

DATA

BUS

BUFFER

This 3-state, bidirectional 8·bit buffer Is used to inter·

face the

8259A

to the system Data Bus. Control words

and status information are transferred through the

Data

Bus Buffer.

READIWRITE

CONTROL

LOGIC

The function of this block is to accept OUTput com·

mands from the

CPU.

It contains the Initialization Com·

mand Word

(ICW)

registers and Operation Command

Word

(OCW)

registers which store the various control

formats for device operation. This function block also

allows

the status of the

8259A

to

be

transferred onto the

Data Bus.

CS

(CHIP

SELECT)

A

LOW

on

this Input enables the

8259A.

No reading or

writing of the chip will occur unless the device is

selected.

WR(WRITE)·

A

LOW

on

this input enables the

CPU

to write control

words

(ICWs

and

OCWs)

to the

8259A.

Fffi

(READ)

A

LOW

on

this Input enables the

8259A

to send the

status

of

the Interrupt Request Register

(IRR),

In

Service

Register

(lSR),

the Interrupt Mask Register

(IMR),

or the

Interrupt level onto the Data

Bus.·

.

9-40

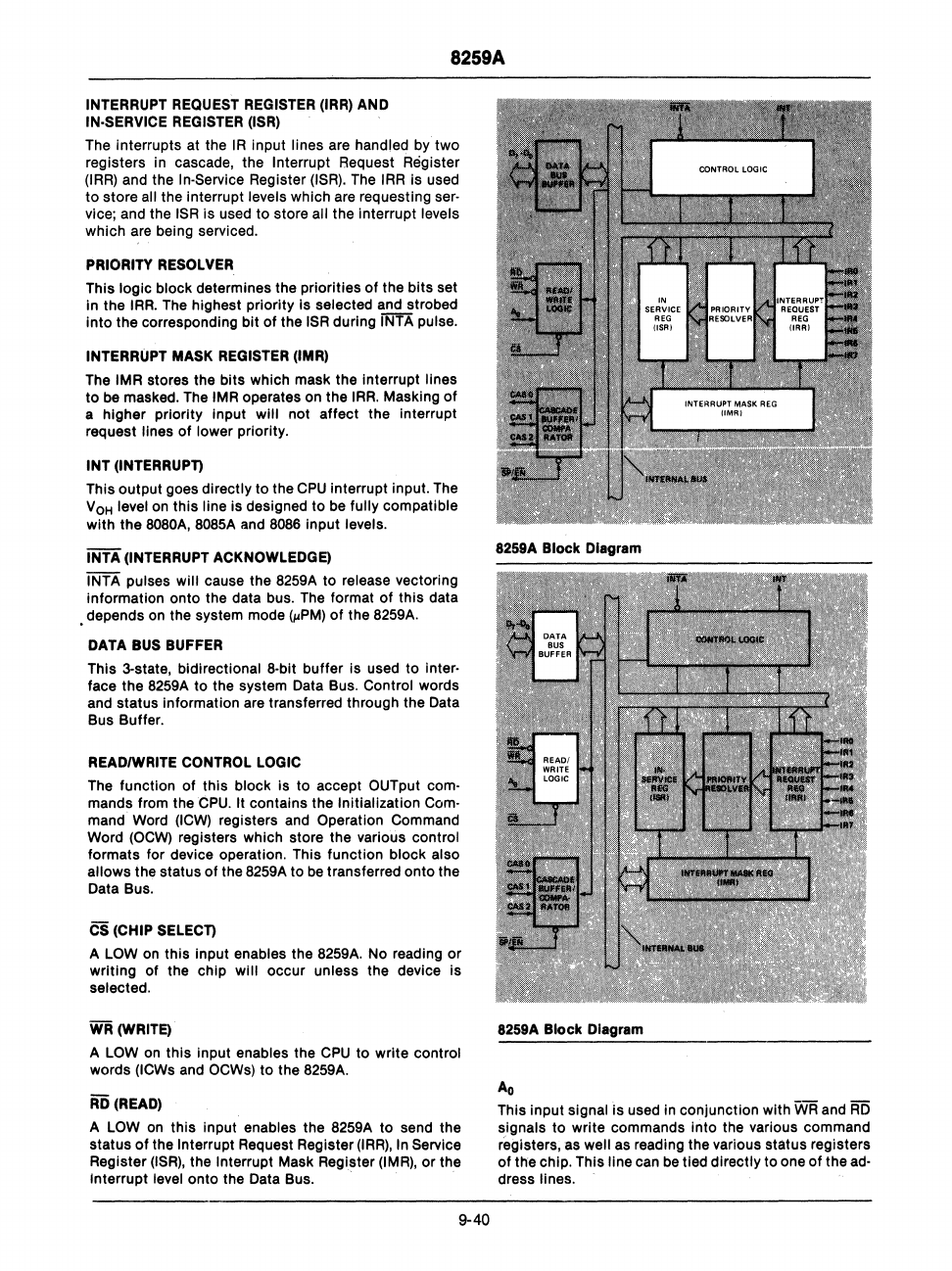

8259A Block Diagram

8259A Block Diagram

Ao

This input signal is used in conjunction with

WR

and

RD

signals to write commands into the various command

registers, as well as reading the various status registers

of the chip. This line can

be

tied directly to one of the ad·

dress lines.