821618226

APPLICATIONS

OF

THE

8216/8226

8080

Data

Bus

Buffer

The

8080

CPU

Data

8us

is

capable

of

driving a single TTL

load and

is

more than adequate for small, single board sys·

tems.

When

expanding such a system

to

more than one board

to

increase

1/0

or Memory size, it

is

necessary

to

provide a

buffer. The

8216/8226

is

a device

that

is

exactly fitted

to

th

is

appl ication.

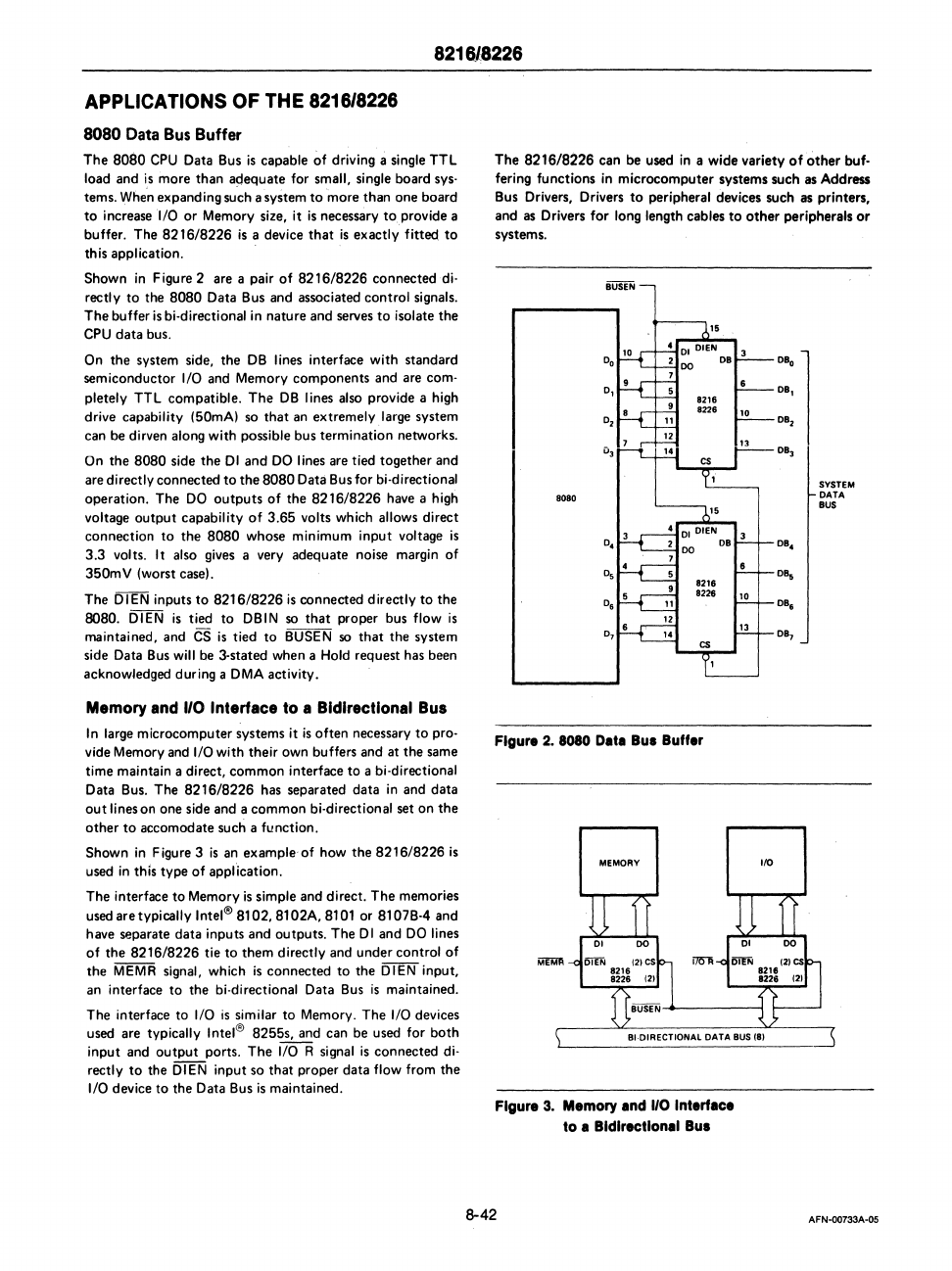

Shown

in

Figure 2 are a pair

of

8216/8226

connected di·

rectly

to

the

8080

Data Bus and associated control signals.

The

buffer

is

bi·directional

in

nature and serves

to

isolate the

CPU

data bus.

On the system side, the

DB

lines interface with standard

semiconductor

liD

and Memory components and are com·

pletely

TTL compatible.

The

DB

lines also provide a high

drive capability

(SOmA)

so

that

an

extremely large system

can be dirven

along with possible bus termination networks.

On

the

8080

side

the

01

and

DO

lines are tied together and

are directly connected

to

the

8080

Data

Bus

for bi·directional

operation. The

DO

outputs

of

the

8216/8226

have a high

voltage

output

capability

of

3.65 volts which allows direct

connection

to

the

8080

whose minimum input voltage

is

3.3 volts. I t also gives a very adequate noise margin

of

350mV (worst case).

The OlEN inputs

to

8216/8226

is

connected directly to the

8080.

DIEN

is

tied

to

DBIN

so

that

proper bus flow

is

maintained, and

CS

is

tied

to

BUSEN

so

that

the system

side Data

Bus

will

be

3-stated when a Hold request has been

acknowledged during a

DMA

activity.

Memory and

1/0

Interface to a Bidirectional

Bus

In

large microcomputer systems it

is

often necessary

to

pro-

vide Memory and liD with their own buffers and at the same

time maintain a direct, common interface to a

bi·directional

Data Bus. The

8216/8226

has separated data

in

and data

out

lines on one side and a

common

bi·directional set on

the

other

to

accomodate such a function.

Shown

in

Figure 3

is

an

example of how

the

8216/8226

is

used

in

this type

of

application.

The interface to Memory

is

simple and direct.

The

memories

used are

typically Intel® 8102,81 02A, 8101 or 8107B·4 and

have separate data inputs and outputs. The 0

I and

DO

lines

of

the 8216/8226 tie

to

them directly and under control of

the

MEMR

signal, which

is

connected

to

the OlEN input,

an interface

to

the bi·directional Data

Bus

is

maintained.

The interface to

liD

is

similar

to

Memory. The

110

devices

used are

typically Intel® 8255s, and can be used for both

input and

output

ports.

The

110

R signal

is

connected di·

rectly

to

the

01

EN

input so

that

proper data flow from the

110

device to the Data Bus

is

maintained.

The

8216/8226

can be used

in

a wide variety

of

other

buf·

fering functions

in

microcomputer systems such as Address

Bus Drivers, Drivers

to

peripheral devices such as printers,

and

as

Drivers for long length cables

to

other

peripherals

or

systems.

BUSEN

15

Do

0,

8216

8226

0,

11

12

",

1.

CS

8080

15

01

OlEN

0,

DO

DB

0,

8216

8226

0,

11

12

0,

1.

cs

FIgure

2.

8080 Data BUI Buffer

MEMORY

FIgure

3.

Memory and

110

Intertace

to

a BIdIrectional BUI

8-42

~l

DB,

,.

DB,

13

DB,

SYSTEM

DATA

BUS

DB,

DB,

10

DB,

13

DB,

I/O

AFN-00733A-05