8293

GENERAL DESCRIPTION

The 8293 is a bidirectional transceiver. It was designed

to interface the

Intel 8291 GPIB Talker/Listener and the

Intel® 8292 GPIB Controller

to

the IEEE Standard

488-1978. Instrumentation Bus (also referred to as the

GPIBBus). The Intel GPIB Bus Transceiver meets or

ex-

ceeds all of the electrical specifications defined in the

IEEE

Standard 488-1978, Seytion 3.3-3.5, including the

required bus termination specifications.

The

8293 can

be

hardware programmed

to

one of four

modes of operation. These modes

allow the 8293

to

be

configured

to

support both a Talker/Listener/Controller

environment and Talker/Listener environment.

In

addi-

tion, the 8293 can

be

used

as

a general purpose three-

state (push-pull) or open-collector bus transceiver with

nine receiver/drivers. Two modes are used

to

support a

Talker/Listener environment

(s.ee

Figure

1),

and to sup-

port a Talker/Listener/Controller environment (see

Figure

2).

Mo.de

1 is the general purpose mode.

TO

PROCESSOR

BUS

14

8291

18

Figure 1. Talker/Listener Configuration

TO

PROCESSOR

BUS

TO

PROCESSOR

BUS

Figure

2.

Talker/Listener/Controller Configuration

GPIB

GPIB

GPIB

GPIB

~[Q)\Yl~OO©[§

000

[F©~

~~'iJ'O©OO

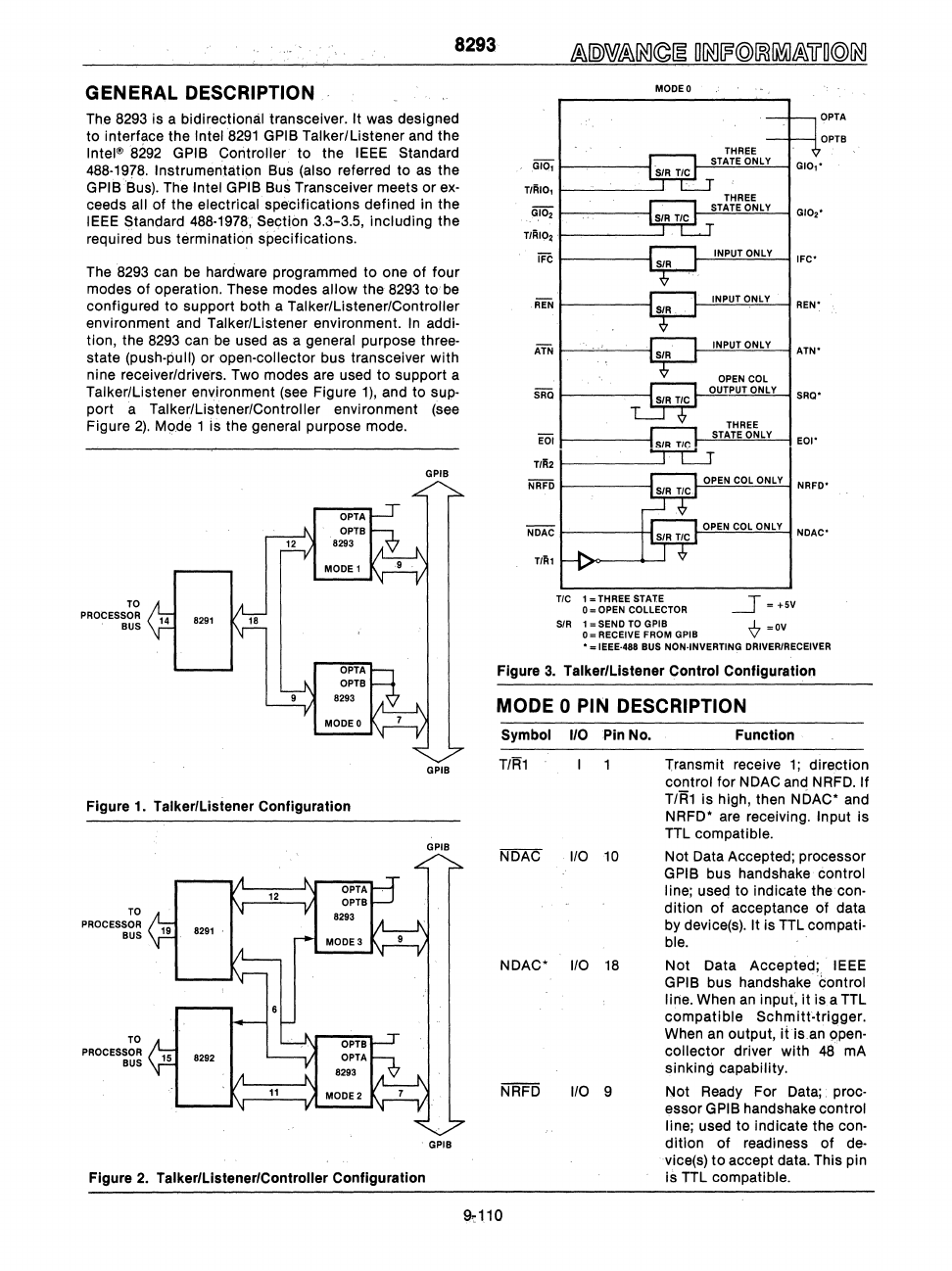

MODEO

OPTA

OPTB

THREE

GIO,

STATE ONLY

GIO,·

TfRIOl

THREE

G.IO,

STATE ONLY

GI02*

TlRIO,

iFc

INPUT ONLY

IFC'

REN

INPUT ONLY

REN'

ATN

INPUT ONLY

ATN'

OPEN COL

SRO

OUTPUT ONLY

SRO'

THREE

WI

STATE ONLY

EOI'

T/~2

N"RFi5

NDAC

T/Rl

TIC 1 = THREE STATE

---.I

=

+5V

0=

OPEN COLLECTOR

SIR

1 = SEND

TO

GPIB

-&

=OV

0=

RECEIVE FROM GPIB

, = IEEE·488 BUS NON·INVERTING DRIVERIRECEIVER

Figure

3.

Talker/Listener Control Configuration

MODE 0 PIN DESCRIPTION

Symbol

1/0

Pin

No_

T/Rl

I/O

10

NDAC*

I/O

18

I/O

9

Function

Transmit receive

1;

direction

control for NDAC and NRFD.

If

TfRl is high, then NDAC* and

NRFD* are receiving.

Input is

TTL compatible.

Not Data Accepted; processor

GPIB bus handshake control

line; used to indicate the

con-

dition of acceptance of data

by device(s).

It is

TTL

compati-

ble.

Not

Data Accepted; IEEE

GPIB

bus handshake control

line.

When

an

input,

it

is a TTL

compatible

Schmitt~trigger.

When

an

output,

ilisan

open-

collector driver with 48 mA

sinking capability.

Not Ready For Data;

proc-

essor GPIB handshake control

line; used

to

indicate the con-

dition

of

readiness of

de-

vice(s)

to

accept data. This pin

is TTL compatible.