SINGLE COMPONENT SYSTEM

8022

Functional Specifications

The

8022's

architecture is based

upon

the 8021,

and

many functions of the two parts are identical.

2.12 Program Memory

The

8022

program memory consists of

2048

words 8 bits wide which are addressed by the

program counter.

The

memory is

ROM

which is

mask

programmable at the factory.

No

external

ROM

expansion capability is provided. There are

three

locations

in

program memory of special

im-

portance.

Location

0: Activating the

RESET

line

of the pro-

cessor causes the first instruction to

be fetched from

location

O.

Location 3: Activating the interrupt input line

(TO)

of the processor (if interrupt is

enabled) causes a jump to subrou-

tine.

Location

7:

A timer / event counter interrupt

re-

sulting from a timer / counter over-

flow

causes a jump to subroutine (if

timer / counter interrupt is

enabled).

Therefore, the first instruction to be executed

after

initialization is stored

in

location 0, the first

word of

an

external interrupt service routine is

stored

in

location 3,

and

the first word of a timer-

/ event counter interrupt service routine is stored

in

location

7.

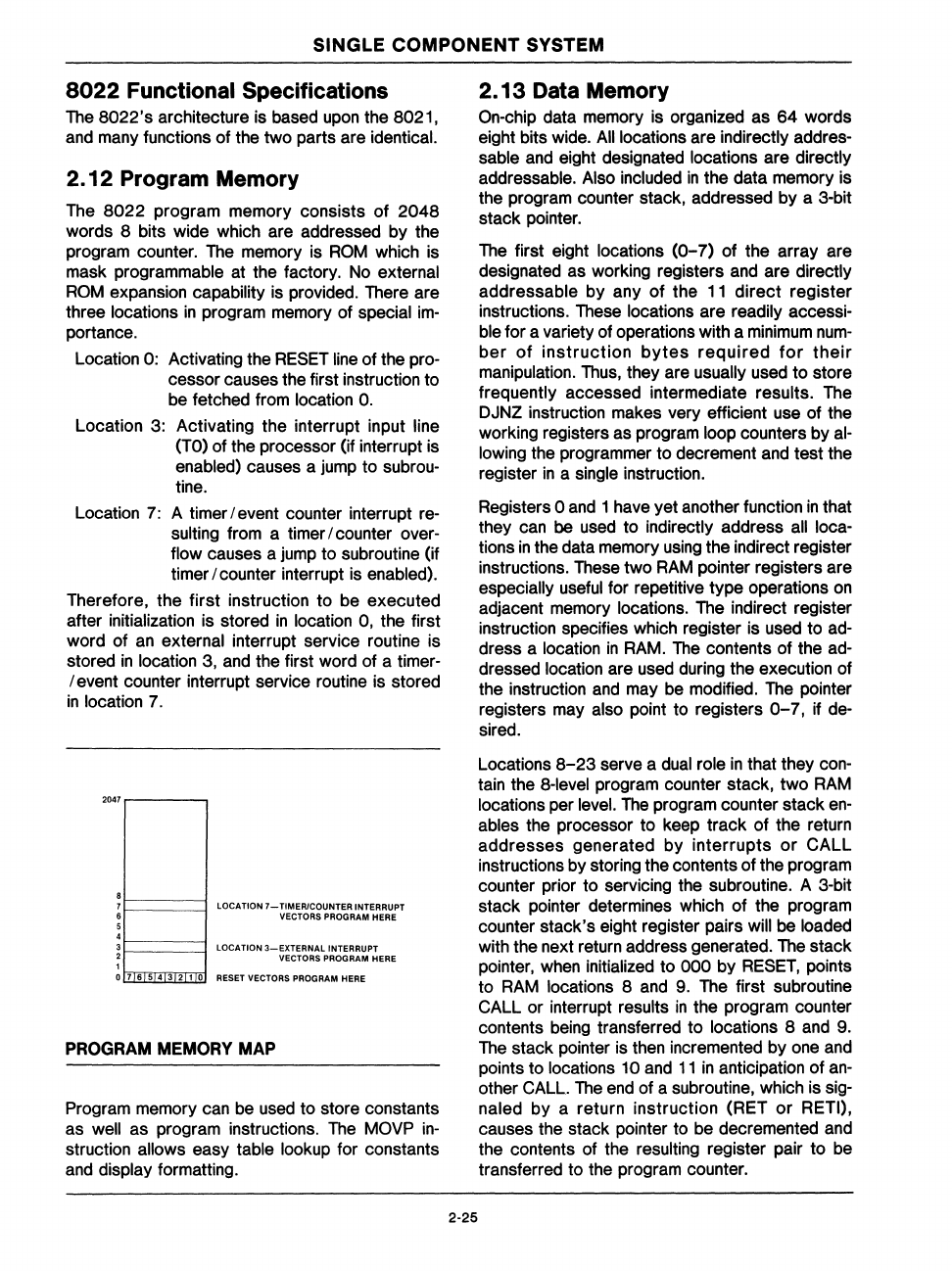

204 7

8

7

6

5

76543210

LOCATION

7 - TIMER/COUNTER INTERRUPT

VECTORS

PROGRAM

HERE

LOCATION

3-EXTERNAL

INTERRUPT

VECTORS PROGRAM HERE

RESEr

VECTORS PROGRAM HERE

PROGRAM MEMORY MAP

Program memory can

be

used

to store constants

as

well as program instructions.

The

MOVP

in-

struction allows easy table lookup for constants

and

display formatting.

2-25

2.13 Data Memory

On-chip data memory is organized as 64 words

eight bits wide.

All

locations are indirectly addres-

sable

and

eight designated locations are directly

addressable. Also included

in

the data memory is

the program counter stack, addressed by a 3-bit

stack pointer.

The

first eight locations

(0-7)

of the array are

designated as working registers

and

are directly

addressable

by any of the

11

direct register

instructions. These

locations are readily accessi-

ble

for a variety of operations with a

minimum

num-

ber

of

instruction

bytes

required

for

their

manipulation.

Thus,

they are usually used to store

frequently accessed intermediate results.

The

DJNZ instruction makes very efficient use of the

working registers as program

loop counters by

al-

lowing the programmer to decrement

and

test the

register

in

a single instruction.

Registers

a

and

1 have yet another function

in

that

they

can

be

used

to indirectly address all loca-

tions

in

the data memory

using

the indirect register

instructions. These two

RAM

pointer registers are

especially

useful for repetitive type operations

on

adjacent memory locations.

The

indirect register

instruction specifies which register is used to

ad-

dress a location

in

RAM.

The

contents of the ad-

dressed location are used during the execution of

the instruction

and

may be modified.

The

pointer

registers may

also point to registers

0-7,

if de-

sired.

Locations

8-23

serve a

dual

role

in

that they

con-

tain the 8-level program counter stack, two

RAM

locations per level.

The

program counter stack

en-

ables the processor to keep track of the return

addresses generated by

interrupts

or

CALL

instructions by storing the contents of the program

counter prior to servicing the subroutine. A 3-bit

stack pointer determines which of the program

counter stack's eight register pairs will be

loaded

with the next return address generated.

The

stack

pointer,

when

initialized to 000 by

RESET,

points

to

RAM

locations 8

and

9.

The

first subroutine

CALL or interrupt

results

in

the program counter

contents

being

transferred to locations 8

and

9.

The

stack pointer is then incremented by

one

and

pOints

to locations 10

and

11

in

anticipation of

an-

other

CALL

The

end

of a subroutine, which is sig-

naled

by a return instruction (RET

or

RETI),

causes the stack pointer to be decremented

and

the contents of the resulting register pair to be

transferred to the program counter.