8022

~rru[§I!..OIMlOIM~rruw

PIN

DESCRIPTION

Designation Pin #

Function.

Designation Pin #

Function

Vss

20 Circuit

GND

p6tential.

RESET

24

Input used to initialize the proc-

essor

by clearing status flip-

Vee

40 + 5V circuit power supply.

flops and setting the program

PROG

37

Output strobe for

Intel@

8243

counter to zero.

I I 0 expander.

AVSS

7

AID

converter

GND

Potential.

POO-P07

10-17

8-bit open-drain port with qoin-

Also establishes the lower limit

Port

0

parator inputs. The switching

of the conversion range.

threshold is set externally by

AVee

3

AID

+ 5V power supply.

VTH.

Optional pull-up resistors

may be added via

ROM mask

SUeST

21

Substrate pin used with a by-

selection. pass capacitor to stabilize the

9

Port 0 threshold reference pin.

substrate voltage and improve

VTH

AID

accuracy.

P10-P17

25-32

8-bit quasi-bidirectional port.

VAREF

4

A

I D converter reference volt-

Port 1

age. Establishes the upper limit

P20-P27

33-36

8-bit quasi-bidirectional port.

of the conversion range.

Port 2

38-39

P20-23

also serve as a 4-bit

ANO,AN1 6,5

Analog inputs to

AID

converter.

1-2

1/0

expander for

Intel@

8243.

Software

selectable

on-chip

TO

8

Interrupt

input and input pin

via

SEL

ANO

and

SEL AN 1

testable using the conditional

instructions.

transfer

instructions

JTO

and

ALE

18

Address Latch Enable. Signal

JNTO.

Initiates

an

interrupt fol-

occurring once every

30 input

lowing a

low level input if inter-

clocks

(once

every

cycle),

rupt

is

enabled.

Interrupt

is

used as

an

output clock.

disabled after a reset.

XTAL

1 22

One side of crystal or inductor

T1

19

Input pin testable using the

JT1

input for internal oscillator. Also

and JNT 1 conditional transfer

input

for

external

frequency

instructions.

Can

be designat-

source. (Not

TTL

compatible.)

ed the timer

I event counter in-

XTAL

2 23

Other side of timing control ele-

put

using

the

STRT

CNT

ment. This

pin

is not connected

instruction. Also serves as the

when

an

external

frequency

zero-cross detection input

to

source is used.

allow zero-crossover sensing

of

slowly moving

AC

inputs. Op-

tional pull-up resistor may be

added via

ROM

mask selection.

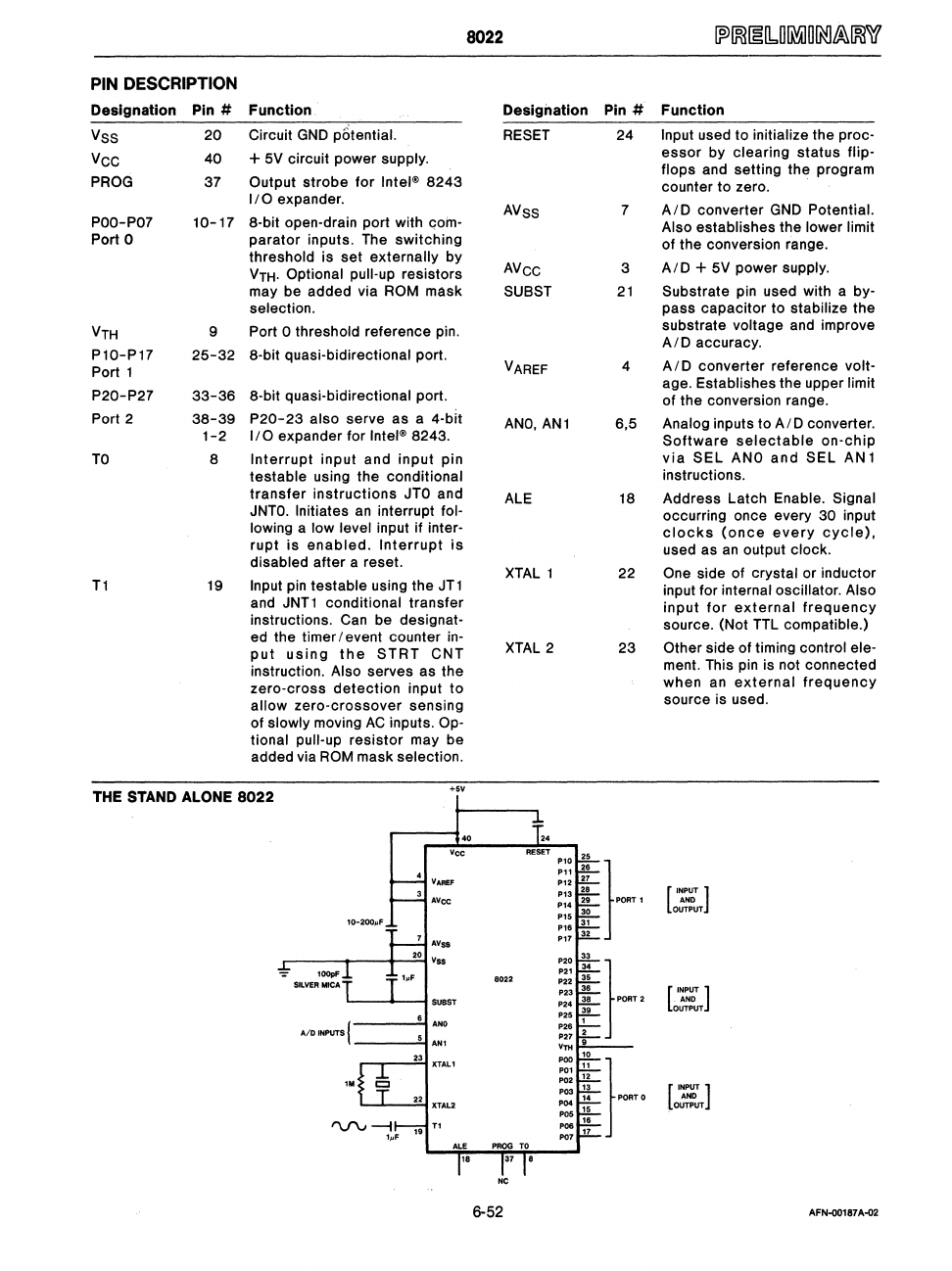

THE STAND ALONE

8022

PI.

2.

}-,

P11

25

V.,..,

P12

27

PI'

28

[

INPUT

]

AVec

..

AND

OUTPUT

10-2oo,u.F

AV

..

2.

Vaa

}-.

l00pF

I,F

8

..

2

SILVER

MICA

P2'

[

WPUT

]

SUBST

P

••

.8

'

AND

••

OUTPUT

P

••

AID

INPUTS

{

AND

P26

P27

ANI

VTN

PDO

I.

}-.

XTAL1

POI

11

PO>

12

1M

P03

13

[

INPUT

]

,.

AND

XTAL2

PDO

,.

.

OUTPUT

PO!

T1

NC

6-52

AFN.(J()187A-QZ