TO

MICROPROCESSOR

INTERFACE

GPIS TRIGGER OUTPU

..E..

..!!

~

~

-.!!.

...!!.

-.!!.

...!!.

2-

---.!

....!.!!.

....!.!.

.2.

--..!.

2-

.....!..

T2

8291

r1L

DO

Di01

01 0102

~

02

0103

30

D!

0104

31

04

0105

32

05

0106

33

06

0107

34

07 0'108

35

CS

OAV

36

Rii

Tlih

1

WR ATN

26

INT

EOI

39

CLOCK TiR2

2

RESET NOAC

38

OREQ

NRFO

37

OACK

SRQ

27

TRIG

lIEN

25

iFC

24

, = GPIS SUS TRANSCEIVER

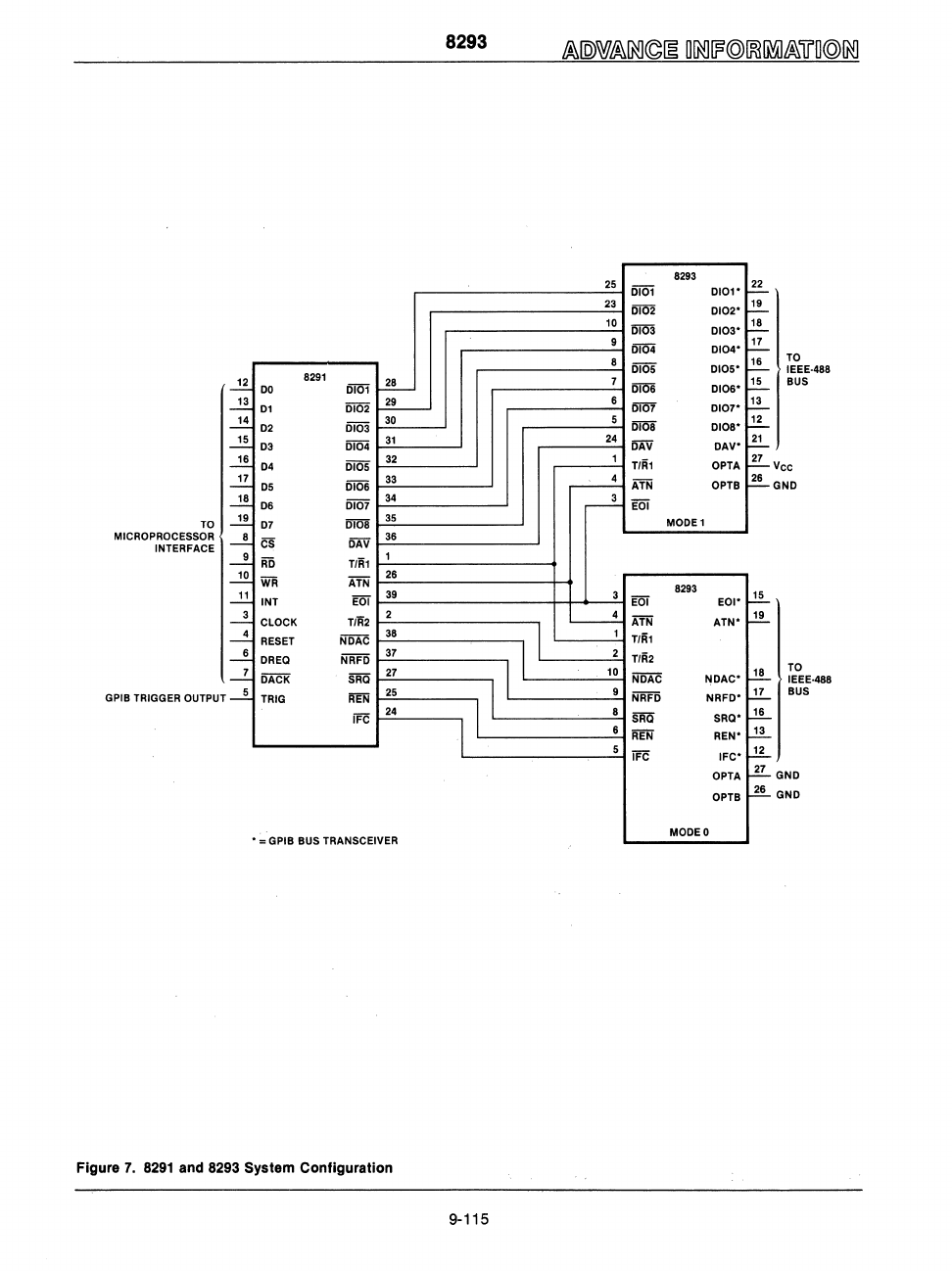

Figure

7.

8291

and 8293 System Configuration

8293

25

23

10

9

8

7

6

5

24

1

~

--.!.

3

~

1

2

10

9

8

6

5

9-115

8293

0101

0101'

Di02

0102'

DiOO

0103'

0104

0104'

0105

0105'

Dii56

0106'

6Im

0107'

!iIl5i

0108'

DAY

OAV'

TIRl

OPTA

ATN OPTS

EOI

MODEl

6293

EOI

EOI'

ATN

ATN'

TIRl

TIR2

NOAC

NOAC'

NRFO

NRFO'

SlIQ

SRQ'

lIEN

REN'

IFC

IFC'

OPTA

OPTS

MOOEO

~

r!!-

..!!...

17

-

..!!...

~

~

~

E-

~

~

..!!..

...!!!...

r!!-

r!!...

r1L

r!!-

r1L

r!!-

~

TO

IEEE·488

SUS

Vee

GNO

TO

IEEE·488

SUS

GNO

GNO