8048/8035L/8748/8748-6/8748-8/8035/8035-8

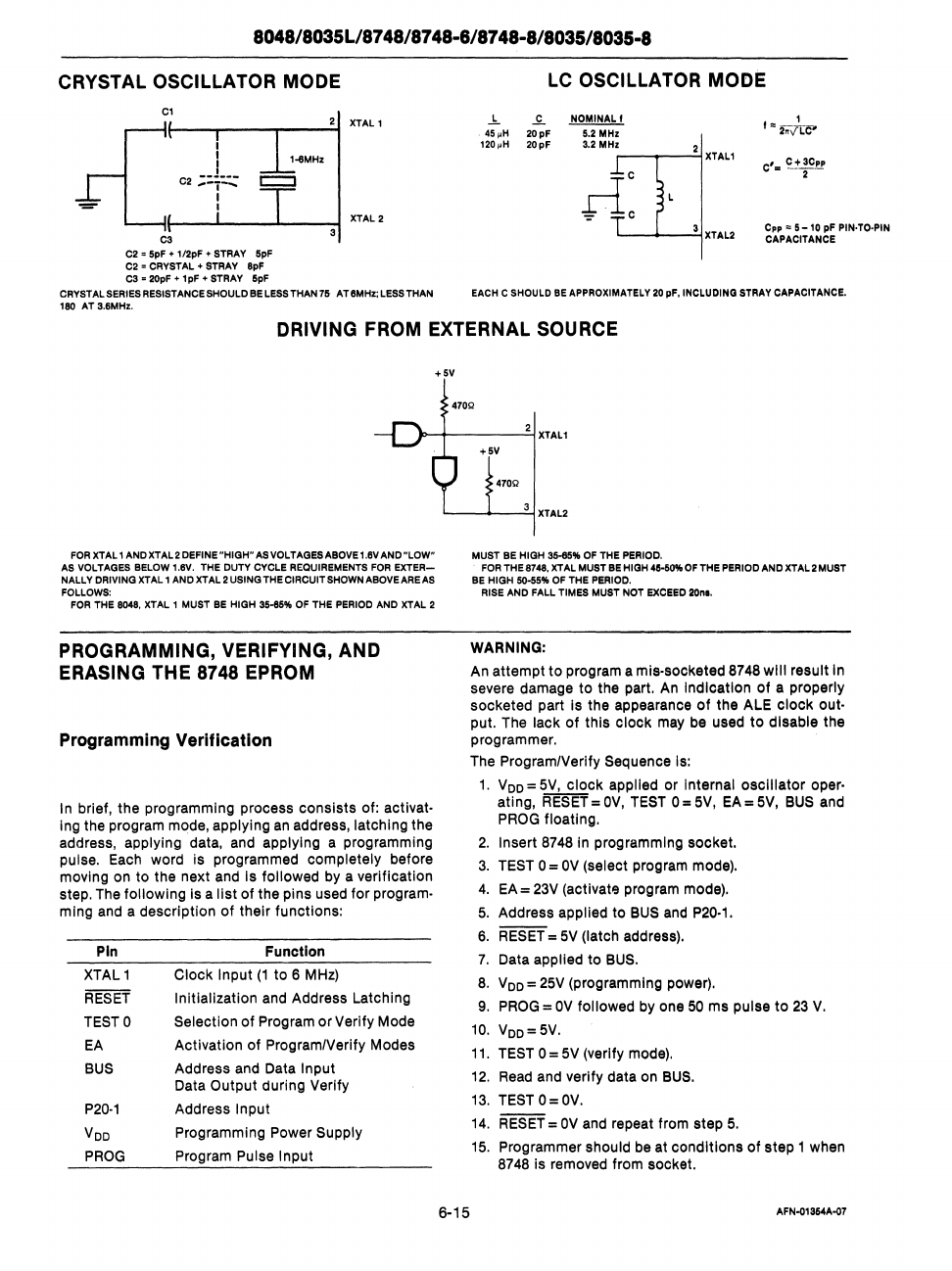

CRYSTAL OSCILLATOR MODE

C1

~

f--""T--...,.---=-t2

XTAL 1

I

HIMHz

C

_-1___

.---.

2

....

-i-...

'---I

I

.....

I

r--~--~--~

XTAL2

C3

C2.

5pF + 1f2pF + STRAY 6pF

C2 • CRYSTAL

+ STRAY 8pF

C3.

20pF + 1pF + STRAY 6pF

CRYSTALSERIES RESISTANCE SHOULO

BE LESS THAN

7&

AT 8MHz: LESS THAN

180 AT

S.BMHz.

LC

OSCILLATOR MODE

.l.

.£.

~

.

45"H

20

pF 5.2 MHz

120"H

20pF

3.2

MHZ.....-_.__-"'l2

XTAL1

L-_

.....

_~3

XTAL2

c •• = 5

-10

pF PIN·TO·PIN

CAPACITANCE

EACH C SHOULD

BE

APPROXIMATELY

20

pF, INCLUDING STRAY CAPACITANCE.

DRIVING FROM EXTERNAL SOURCE

+SV

47012

10-+-

____

2

=-1

XTAL1

FOR XTAL 1

ANDXTAL2DEFINE"HIGH"

ASVOLTAGESABOVE 1.8VAND

"LOW"

AS VOLTAGES BELOW 1.8V. THE DUTY CYCLE REQUIREMENTS FOR

EXTER-

NALLY DRIVING XTAL 1 AND XTAL 2 USING THE CIRCUIT SHOWN ABOVE ARE

AS

FOLLOWS:

FOR

THE 8046, XTAL 1 MUST BE HIGH

35-85'110

OF

THE

PERIOD AND XTAL 2

PROGRAMMING, VERIFYING, AND

ERASING THE 8748 EPROM

Programming Verification

In

brief, the programming process consists of: activat·

ing the program mode, applying

an

address, latching the

address,

applying data,

and

applying a programming

pulse.

Each

word is programmed compietely before

moving on to the next and

is

followed by a verification

step. The

following is a list

of

the pins used for program-

ming

and

a description

of

their functions:

Pin

Function

XTAL1

Clock Input

(1

to 6

MHz)

AESET

Initialization and Address Latching

TEST

0

Selection

of

Program or Verify Mode

EA

Activation

of

ProgramlVerify Modes

BUS

Address and Data Input

Data Output during Verify

P20-1

Address Input

Voo

Programming Power Supply

PAOG

Program Puise Input

+5V

470Q

L-_

.....

_....:

3

"'XTAL2

6-1S

MUST BE HIGH

36-85'110

OF

THE PERIOD.

. FOR THE 8748. XTAL MUST BE HIGH

48-t10'II0

OFTHE

PERIOD AND XTAL 2 MUST

BE HIGH

50-65'110

OF THE PERIOD.

RISE

AND FALL TIMES MUST NOT EXCEED IOn ••

WARNING:

An

attempt

to

program a mis-socketed

8748

wlil result

In

severe damage

to

the part.

An

indication

of

a properly

socketed part is the appearance

of

the ALE clock out-

put. The lack

of

this clock

may

be

used

to

disable the

programmer.

The ProgramlVerify

Sequence

Is:

1.

Voo

=

SV,

clock applied or internal oscillator oper-

ating, AESET=OV,

TEST

O=SV, EA=SV,

BUS

and

PAOG

fioating.

2.

Insert

8748

in programming socket.

3.

TEST

0 =

OV

(select program mode).

4.

EA

=

23V

(activate program mode),

S.

Address applied to

BUS

and

P20-1.

6.

AESET

=

SV

(latch address).

7.

Data applied to

BUS.

8.

Voo

=

2SV

(programming power).

9.

PAOG

=

OV

followed by one

SO

ms pulse

to

23

V.

10.

Voo=SV.

11.

TEST

0 =

SV

(verify mode).

12.

Read

and verify data on

BUS.

13.

TEST

O=OV.

14.

FiES'E'f

=

OV

and repeat from step

S.

1S.

Programmer should

be

at conditions

of

step 1 when

8748

is removed from socket.

AFN..Q1364A..Q7