8031/8051/8751

Program Crystal

Or

Data Frequency

Category

1.0. Description

Comments Memory

MHz

(Max)

I/O

Expander

8

Line

I/O

Expander

Low

Cost

I/O

Expander

12

(Shift

Register)

Standard

EPROMs

2758

1 K x 8

450 ns

Light

User

programmable

and

P

9

Erasable

erasable.

2716-1

2K

x 8 350 ns

Light

P

11

Erasable

2732

4K x 8

450 ns

Light

P

9

Erasable

2732A

4K

x 8 250 ns

Light

P 12

Erasable

Standard

RAMs

2114A

1Kx4100nsRAM

Data

memory

can be

D 12

2148

1 K x 4

70 ns RAM

easily

expanded

using

D 12

2142-2

1 K x 4

200 ns RAM

standard

NMOS

RAMs.

D 12

"'

C

Multiplexed

Address/

8185A

1 K x 8 300 ns RAM

D 12

<Il

Data

RAMs

c

0

a.

E

Standard

I/O

8212

8-Bit

I/O

Port

Serves as

Address

Latch

D

12

0

8282

8-Bit

I/O

Port

or

I/O

port.

D 12

U

01)

8283

8-Bit

I/O

Port

D 12

co

8255A

Programmable

Three

8-bit

programmable

D 12

23

co

Peripheral

Interface

I/O

ports.

en

8251A

Programmable

Com-

Serial

Communications

D 12

U

munications

Interface

Receiver/Transmitter.

:2

<11

:0

Standard

Peripherals

8205 1

of

8

Binary

Decoder

MCS-80

and

MCS-85

D

12

~

8286

Bi-directional

Bus

Driver

peripheral

devices are

D

12

a.

8287

Bi-directional

Bus

Driver

compatible

with

the 8051

D

12

E

0

(Inverting)

allowing

easy

addition

of

U

8253A

Programmable

Interval

specialized

interfaces.

D

12

Timer

Future

MCS-80/85

8279

Programmable devices

will

also

be

D

12

Keyboard/Display

compatible.

Interface

(128 Keys)

8291

GPIB

Talker/Listener

D

12

8292

GPIB

Controller

D

11.7

Universal

Peripheral

8041A

ROM

Program

Memory

User

programmable

to

D/P

12/11.7

Interfaces

8741A

EPROM

Program

perform

custom

I/O

and

D/P

12/11.7

Memory

control

functions.

Memories

with

8155-2

256 x 8

330

ns

RAM

D

12

on-chip

I/O

and

8355-2

2K

x 8 330 ns

ROM

P

11.6

Peripheral

Functions.

8755-2

2K

x 8 330 ns

EPROM

P

11.6

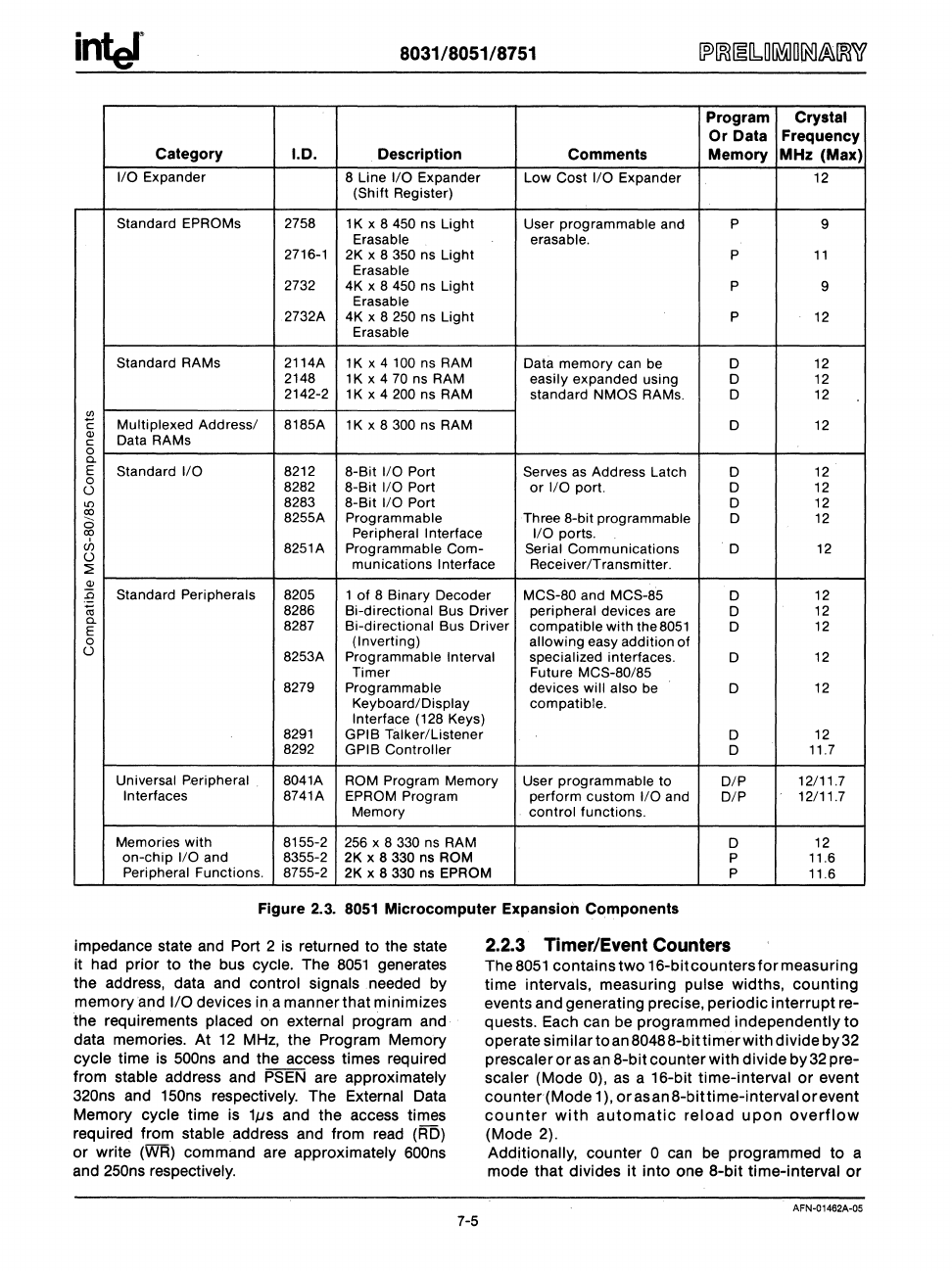

Figure 2.3. 8051 Microcomputer Expansion Components

impedance state and Port 2

is

returned to the state

it had prior

to

the bus cycle. The

8051

generates

the address, data and

control signals needed by

memory and

I/O devices

ina

manner that minimizes

the requirements

placed on external program and

data memories. At

12

MHz, the Program Memory

cycle time

is

500ns and the access times required

from

stable address and PSEN are approximately

320ns and 150ns respectively. The External Data

Memory

cycle time is

1J,Js

and the access times

required from

stable address and from read (RD)

or

write

(WR)

command are approximately 600ns

and 250ns respectively.

7-5

2.2.3 Timer/Event Counters

The

8051

contains

two

16-bitcountersformeasuring

time intervals, measuring pulse widths,

counting

events and generating precise,

periodic

interrupt

re-

quests. Each can

be

programmed independently

to

operate similar

toan

80488-bittimerwith

divide

by32

prescaler

or

as

an

8-bit counter with divide by

32

pre-

scaler (Mode 0),

as

a 16-bit time-interval

or

event

counter

(Mode 1),

or

as

an

8-bittime-interval

orevent

counter

with

automatic

reload

upon

overflow

(Mode 2).

Additionally, counter

0

can

be

programmed

to

a

mode

that

divides

it

into

one

8-bit

time-interval

or

AFN-01462A~05