8048/8035L/87 48/87 48·6/8035

SINGLE COMPONENT 8·BIT MICROCOMPUTER

• 8048 Mask Programmable

ROM

• 8035L

CPU

Only

with

Power Down Mode

• 8748 User Programmable EPROM

• 8748·6 Up

to

55C 8748

• 8035

CPU

Only (No Power Down Mode)

• 8·BIT

CPU,

ROM,

RAM,

1/0

in Single

Package

• Interchangeable

ROM

and

EPROM

Versions

• 1 K x 8 ROMIEPROM

64x

8

RAM

27110

Lines

• Interval TimerlEvent Counter

• Single

5V

Supply

•

Easily Expandable Memory and

1/0

•

2.5

fJsec

and

5.0

fJsec

Cycle Versions

All Instructions 1 or 2 Cycles.

• Over

90

Instructions: 70% Single Byte

• Compatible with

808018085

Series,

Peripherals

• Single Level Interrupt

The Intel 8048/8748/8743-6/8748-B/8035/B035-8 are totally self-sufficient, 8-blt parallel computers fabricated on single

silicon chips using Intel's N-channel silicon gate MOS process.

The

B048

contains a 1 K x B program memory, a 64 x B RAM data memory,

27

I/O

lines, and

an

8-blt timer/counter in addi-

tion

to

on-board oscillator and clock circuits. For systems that require extra capability, the 8048 can be expanded using

standard memories and

MeS-BO /MeS-B5 peripherals. The 8035 Is the equivalent

of

an

8048 without program memory

and can be used with

external ROM and RAM. The B035L has the RAM power-down mode

of

the

804B

while the 8035 does

not. The 8748-6 is a 6 MHz

B74B

up

to

55e. To reduce development problems

to

a minimum and provide maximum flexi-

bility, three interchangeable pin-compatible versions

of

this single component microcomputer exist: the 8748 with user-

programmable

and erasable EPROM program memory

for

prototype and preproduction systems, the

B04B

with factory-

programmed mask ROM program memory

for

low cost, high

VOlume

production, and the

B035

without program memory

for

use with external program memories.

These microcomputers are designed

to

be efficient controllers

as

weil

as

arithmetic processors. They have extensive bit

handling capability

as

weli

as

facilities for both binary and

BeD

arithmetic. Efficient use

of

program memory results from

an

instruction set consisting mostly

of

single bit instructions and no instructions over 2 bytes in length.

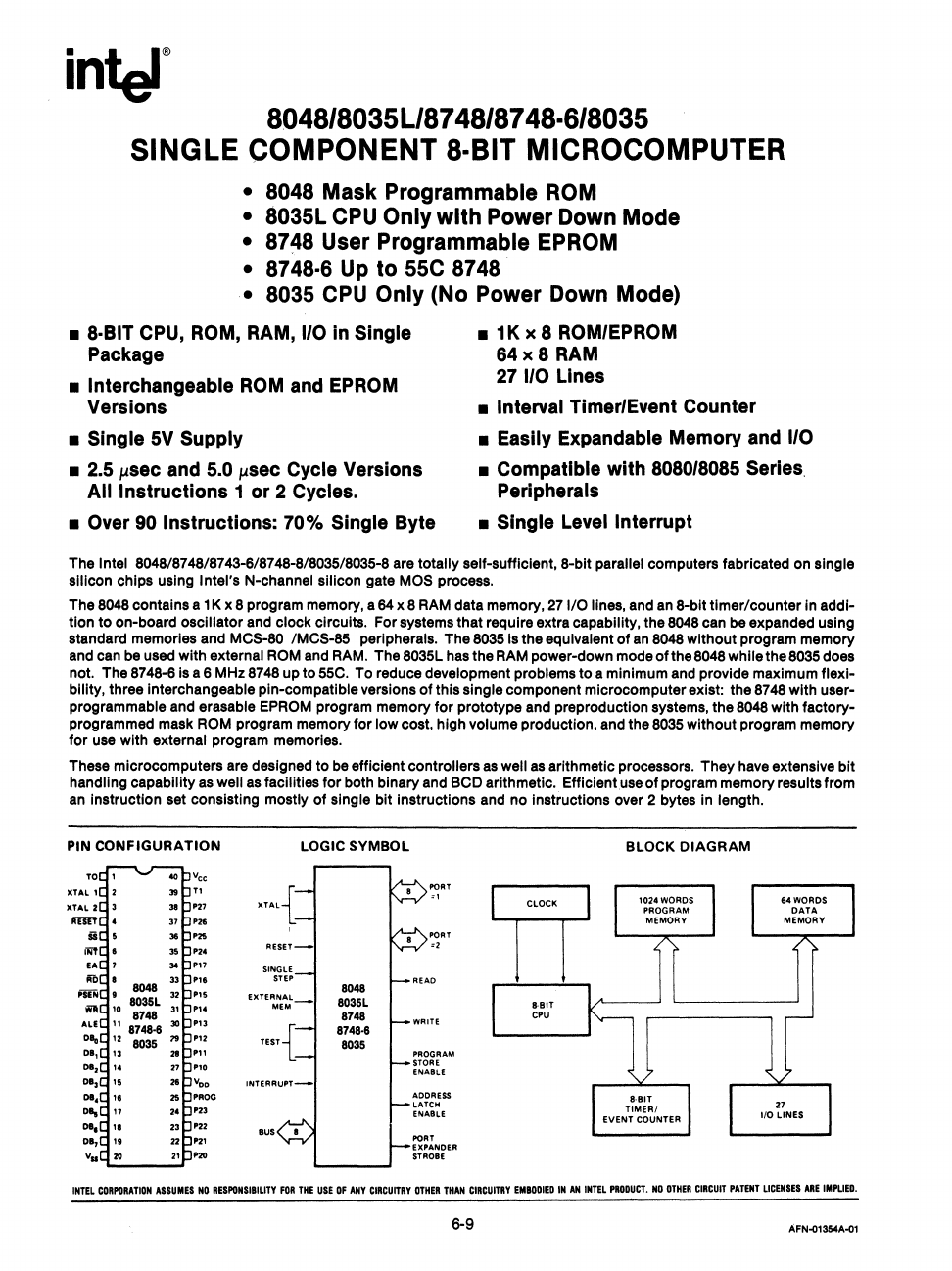

PIN CONFIGURATION

LOGIC SYMBOL

8048

8035L

8748

8748·6

8035

ADDRESS

L.ATCH

ENABLE

PORT

EXPANDER

STROBE

BLOCK DIAGRAM

INTEL

CORPORATION

ASSUMES

NO

RESPONSIBILITY

FOR

THE

USE

OF

ANY

CIRCUITRY

OTHER

THAN

CIRCUITRY

EMBOOIEO

IN

AN

INTEL

PROOUCT.

NO

OTHER

CIRCUIT

PATENT

LICENSES

ARE

IMPLIEO.

6-9

AFN.Q1354A.Ql