SINGLE

COMPONENT

SYSTEM

Device Testable

Jump Conditions

(Jump On)

Accumulator

Accumulator

Bit

Carry

Flag

All

zeros

User

Flags

(FO,

F1)

Timer Overflow Flag

Test

Inputs

(TO,

T1)

.Interrupt Input (INT)

JTF

EX

ECUTEO--.:r--.

RESET

>--+--1

R

TIMER INT

___

....

-.

RECOGNIZED

EXECUTED

mT~

______

~

PIN

ALE---I-'"

S

R

R

0

°

°

°

TIMER

FLAG

TIMER

OVERFLOW

FF

TIMER

INT

ENABLE

INT

FF

CLK

LAST CYCLE

}-

____

....l

OF

INST.

DISI

EN

I

EXECUTED

EXECUTED

RESET---:&..._

INTERRUPT

LOGIC

S

INT

ENABLE

R

not all

Q

Q

Q

Q

Q

zeros

1

1

1

1

1

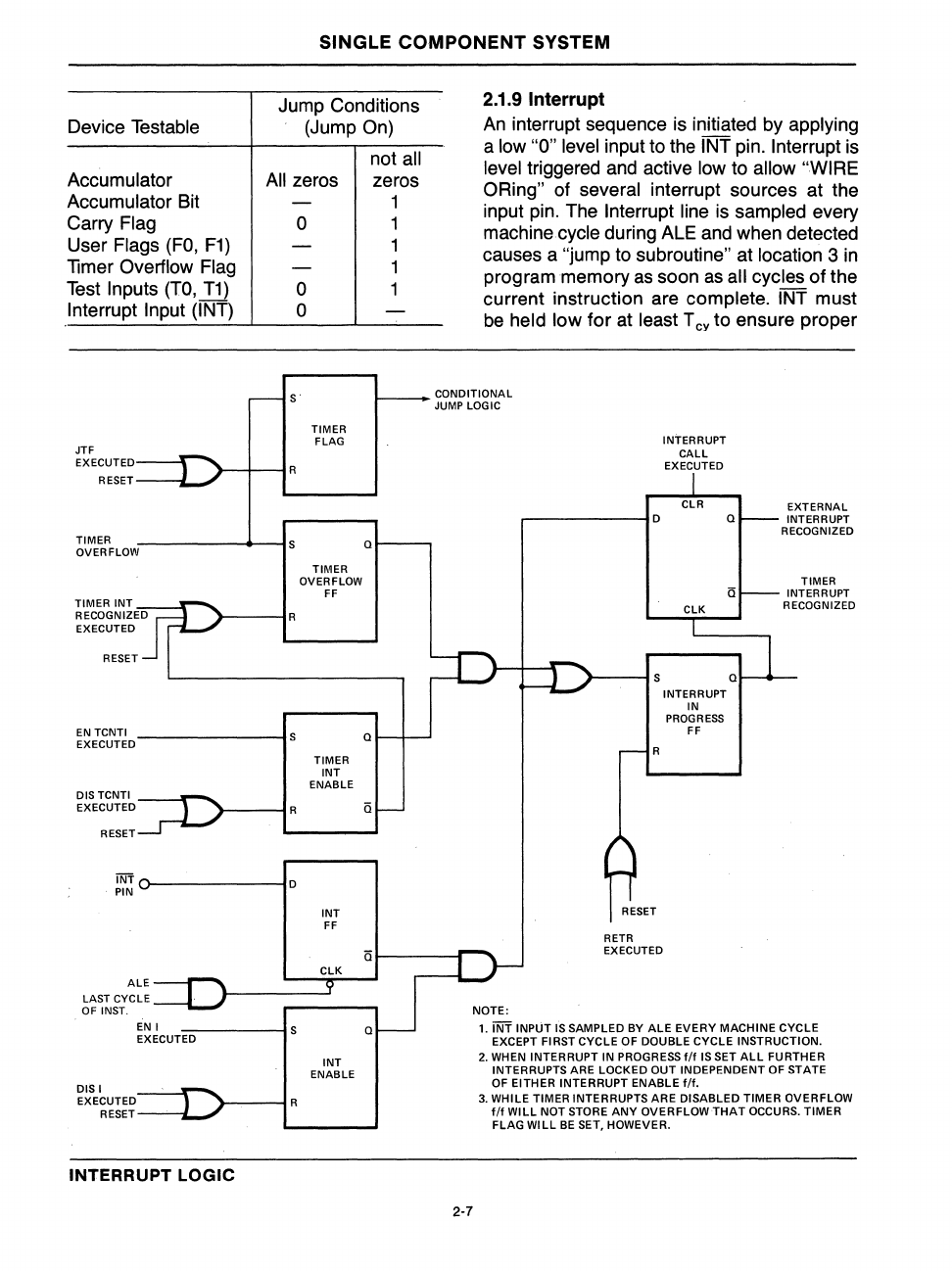

2.1.9 Interrupt

An

interrupt sequence is initiated by applying

a low "0" level input to the INT pin. Interrupt

is

level triggered and active low to allow "WIRE

DRing"

of several interrupt sources at the

input pin. The

Interrupt line is sampled every

machine

cycle during ALE and when detected

causes a "jump to subroutine" at location 3

in

program memory

as

soon

as

all cycles

of

the

current instruction are

complete. INT must

be

held low

for

at least T

Cy

to ensure proper

CONDITIONAL

JUMP

LOGIC

2-7

NOTE:

INTERRUPT

CALL

EXECUTED

CLR

r-------I

D Q

S

R

RESET

RETR

EXECUTED

Q

INTERRUPT

IN

PROGRESS

FF

EXTERNAL

INTERRUPT

RECOGNIZED

TIMER

INTERRUPT

RECOGNIZED

1.

INT

INPUT IS SAMPLED BY

ALE

EVERY

MACHINE

CYCLE

EXCEPT FIRST CYCLE

OF

DOUBLE

CYCLE

INSTRUCTION.

2.

WHEN

INTERRUPT

IN

PROGRESSf/f

ISSET

ALL

FURTHER

INTERRUPTS ARE

LOCKED

OUT

INDEPENDENT

OF STATE

OF EITHER

INTERRUPT

ENABLE

f/f.

3.

WHILE TIMER INTERRUPTS

ARE

DISABLED

TIMER

OVERFLOW

f/f

WILL

NOT STORE

ANY

OVERFLOW

THAT

OCCURS.

TIMER

FLAG

WILL

BE

SET, HOWEVER.