8291

When the

8291

is addressed

to

talk, it uses the data-out

register

to

move data onto the GPIB. Upon a write to this

register, the

8291

initiates and completes the handshake

while sending the byte out over the bus. When the

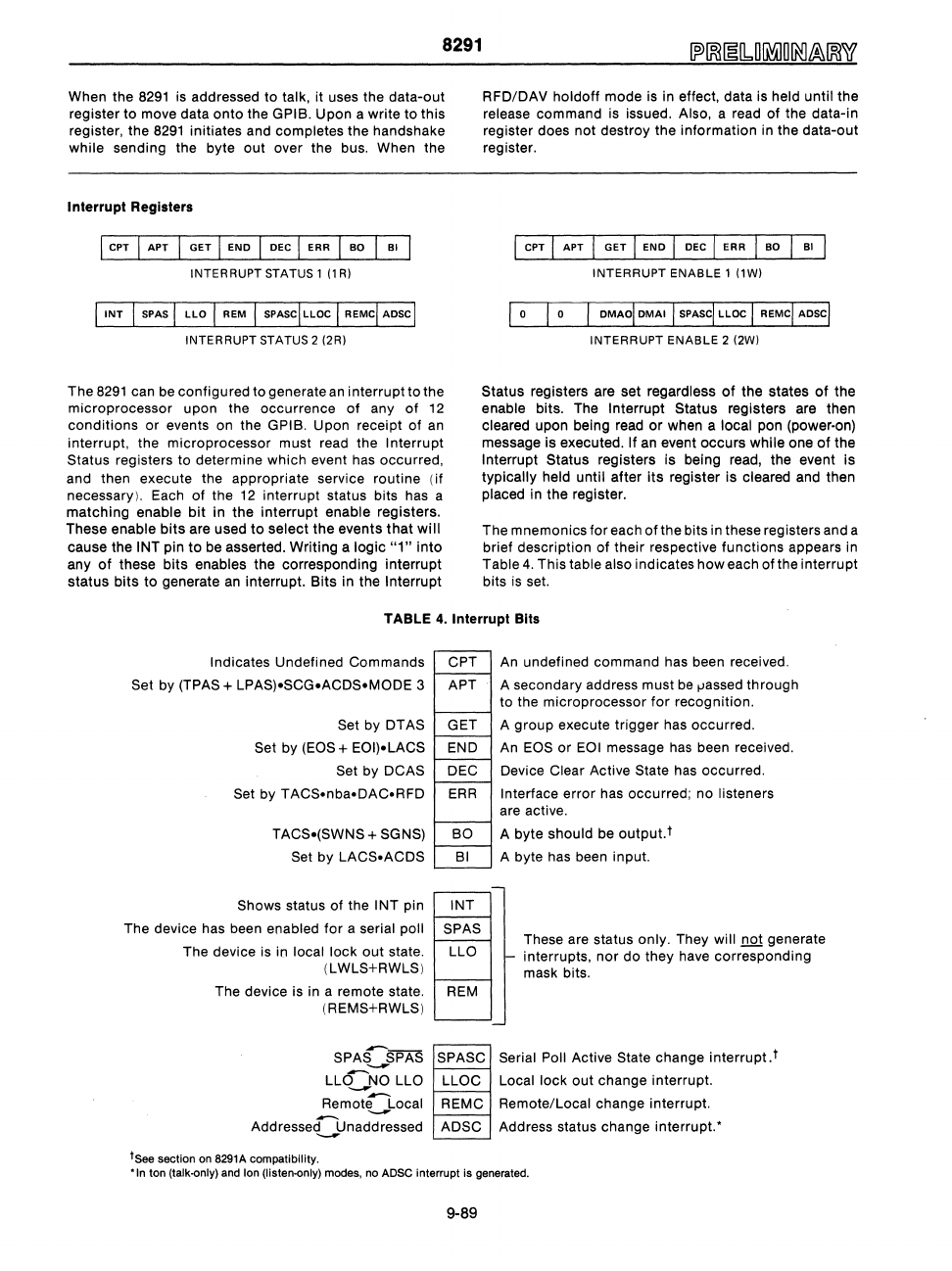

I nterrupt Registers

I

CPT

I

APT

I

GET

I

ENO

OEC

I

ERR

BO

BI

INTERRUPT STATUS 1

II

R)

liNT

I

SPAS

I

LLO

I

REM

I SPAscl

LLOC

I

REMCI

ADSC

I

INTERRUPT STATUS 2

12R)

The

8291

can be configured to generate

an

interrupt

to

the

microprocessor upon the occurrence

of

any of

12

conditions

or

events on the GPIB. Upon receipt of

an

interrupt, the microprocessor must read the Interrupt

Status

registers to determine which event has occurred,

and then execute the appropriate service routine (if

necessary). Each of the

12

interrupt status bits has a

matching enable bit in the interrupt enable registers.

These enable

bits

are used

to

select the events

that

will

cause the INT pin

to

be asserted. Writing a logic

"1"

into

any

of

these bits enables the corresponding interrupt

status bits to generate

an

interrupt. Bits in the Interrupt

RFO/OAV

holdoff mode

is

in effect, data is held until the

release command is issued. Also, a read of the data-in

register does not destroy the information in the data-out

register.

I

CPT

I

APT

I

GET

I

END

I

DEC

I

ERR

BO

BI

I

INTERRUPT ENABLE 1 I1W)

I 0 I 0 I

DMAOI

DMAI

I SPAscl LLOC I

REMCI

ADscl

INTERRUPT ENABLE 2 (2W)

Status registers are set regardless

of

the states

of

the

enable bits. The

Interrupt Status registers are then

cleared upon being read

or

when a local pon (power·on)

message is executed. If

an

event occurs while one

of

the

Interrupt Status registers is being read, the event is

typically held until after its register is cleared and then

placed in the register.

The mnemonics for each of the bits in these registers and a

brief description of their respective functions appears in

Table

4.

This table also indicates how each of the interrupt

bits

is

set.

TABLE

4.

Interrupt Bits

Indicates Undefined Commands

Set by (TPAS + LPAS)oSCGoACOSoMODE 3

Set by DTAS

Set

by

(EOS

+ EOI)oLACS

Set

by OCAS

Set

by TACS.nbaoOAC.RFO

TACSo(SWNS

+ SGNS)

Set

by LACS.ACOS

Shows

status of the INT pin

The device has been enabled

for

a serial poll

The device is in local lock out state.

(LWLS+RWLS)

The device is in a remote state.

(REMS+RWLS)

CPT

APT

GET

END

DEC

ERR

BO

BI

'----

INT

SPAS

LLO

~

An

undefined command has been received.

A secondary address must

be

""assed

through

to the microprocessor

for

recognition.

A group execute trigger has occurred.

An

EOS

or

EOI

message

has

been received.

Device Clear Active

State has occurred.

Interface error has occurred; no listeners

are active.

A byte should be output.

t

A byte has been input.

I-

These are status only. They will not generate

interrupts,

nor

do they have corresponding

mask bits.

SPAS-SPAS

SPASC Serial Poll Active State change

interrupt.t

---

LLCNO

LLO LLOC Local lock out change interrupt.

Remoti:~Jocal

REMC Remote/Local change interrupt.

AddressedUnaddressed

AOSC Address status change

interrupt:

--

tSee

section on 8291A compatibility.

'In

ton (talk-only) and Ion (listen·only) modes, no ADSC interrupt Is generated.

9-89