inter

8155/8156/8155-2/8156-2

2048

BIT

STATIC MOS RAM WITH

I/O

PORTS AND TIMER

8085A

8085A-2

8155

8155-2

8156

8156-2

•

2S6

Word x 8 Bits

• Single

+5V

Power Supply

• Completely

Static Operation

• Internal Address Latch

• 2 Programmable 8 Bit 1/0 Ports

~

CPU Chip

. Enable

ACTIVE LOW

ACTIVE HIGH

• 1 Programmable 6-Bit

1/0

Port

• Programmable 14-Bit Binary

Counterl

Timer

• Multiplexed Address and Data Bus

•

40

Pin DIP

The 8155 and 8156 are RAM and

I/O

chips

to

be used in the MCS-85'· microcomputer system. The RAM portion is designed

with

2048 static cells organized as 256 x

8.

They have a maximum access time

of

400 ns to permit use with

no

wait states

in

8085A CPU. The 8155-2 and

13156-2

have maximum access times

of

330 ns for use with the 8085A-2.

The

110

portion consists

of

three general purpose

110

ports. One

of

the three ports can be programmed

to

be status pins,

thus

allowing the other

two

ports

to

operate in handshake mode.

A 14-bit programmable

counter/timer

is also included on chip to provide either a square wave

or

terminal

count

pulse

for

the CPU system depending on timer mode.

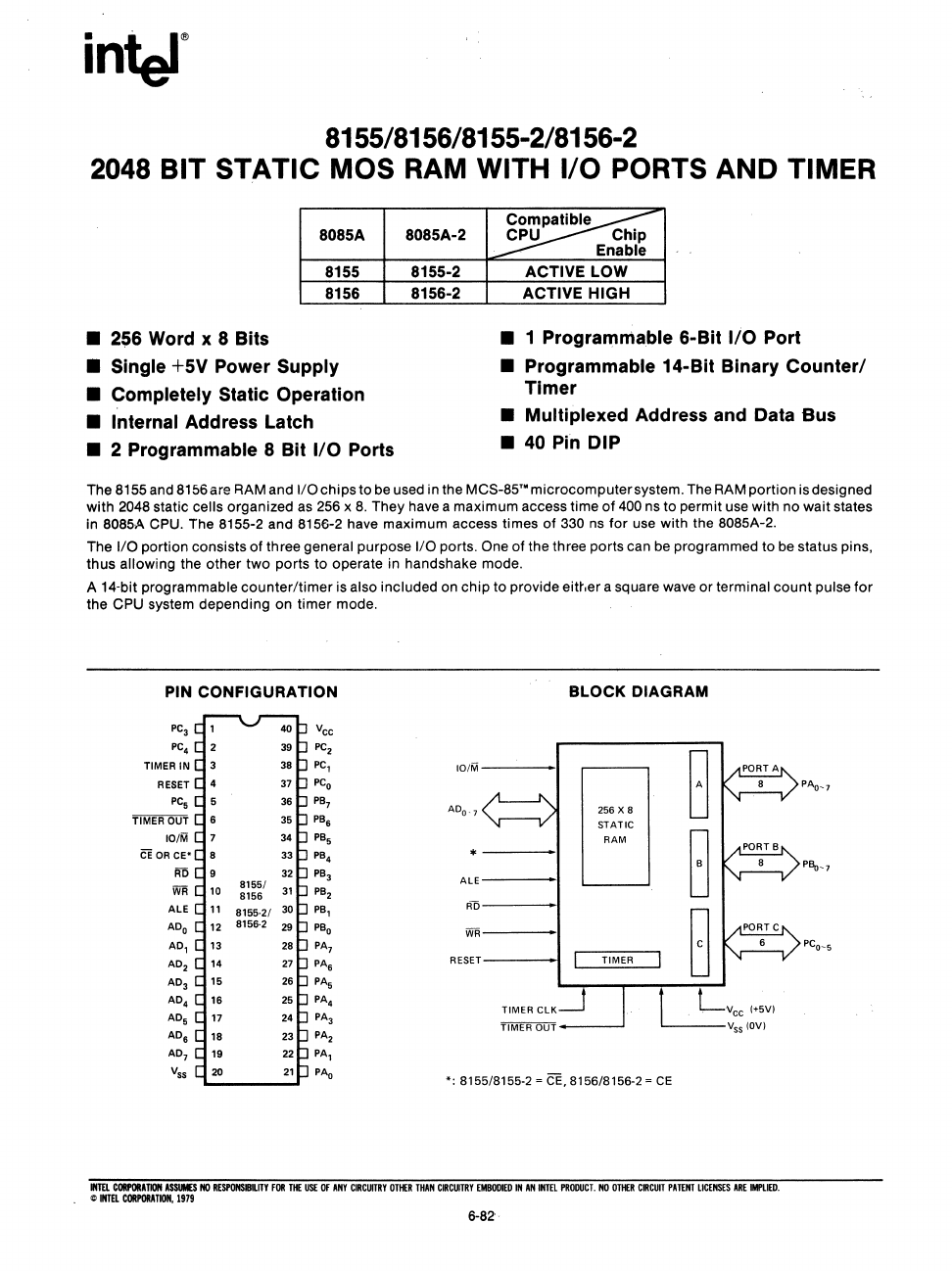

PIN CONFIGURATION

BLOCK DIAGRAM

pc.

vee

pc.

pC

z

G

TIMER

IN

PC,

101M

PORT A

RESET

PC

o

a

PC.

PB,

ADO-7

256 X a

TIMER OUT

PBs

STATIC

101M

PBs

RAM

G

CE

OR CE*

PB.

*

ifD

PB.

ALE

WR

PB

z

ALE

PB,

AD

B

ADo

PB

o

WA

AD,

PA,

ADz

PAs

RESET TIMEA

AD.

PAs

Lvcc

!+5V)

AD.

PA.

TIMER

eLK

AD.

PA.

ADa

TIMER OUT

Vss

IOVI

PAz

AD,

PA,

v

••

PAs

*:

8155/8155-2 =

CE,

8156/8156-2 =

CE

IllEL

_1I0Il_5

NO

RE1I'IJIISIIlITY

FOR

TI£

USE

OF

ANY

CIlCUITRI

OTi£R

THAN

CIIClml

EMBODEO

IN

AN

IllEL

PRODUCT.

NO

IlTHDI

CIlCUIT

PATENT

UCENSES

ARE

_10.

"IIIEL

_lION.

1979

6-82"

PAs-,

ps,,-,

PC

O

-

5