8273, 8273-4, 8273·8

PROGRAMMABLE

HOLC/SOLC

PROTOCOL

CONTROLLER

•

CCITT

X.25

Compatible

•

Programmable N

RZI

Encode/ Decode

•

HDLC/SDLC Compatible

•

Two User Programmable Modem

•

Full Duplex, Half Duplex, or Loop

Control Ports

SDLC Operation

•

Digital Phase Locked Loop Clock

•

Up

to

64K Baud Synchronous

Recovery

Transfers

Minimum

CPU

Overhead

•

•

Automatic FCS

(CRC)

Generation and

Checking

•

Fully Compatible with 8048/8080/8085/

Up

to

9.6K Baud

with

On·Board Phase

8088/8086

CPUs

•

Locked Loop

•

Single

+5V

Supply

The

Intel@

8273

Programmable HOLC/SOLC Protocol Controller is a dedicated device designed

to

support the ISO/

CCITT's

HOLC and IBM's SOLC communication line protocols. It is fully compatible with Intel's new high performance

microcomputer systems such as the

MCS-88/86™.

A frame level command set is achieved

by

a unique microprogrammed

dual processor chip architecture. The processing capability supported

by

the

8273

relieves the system

CPU

of

the low

level real-time

tasks normally associated with controllers.

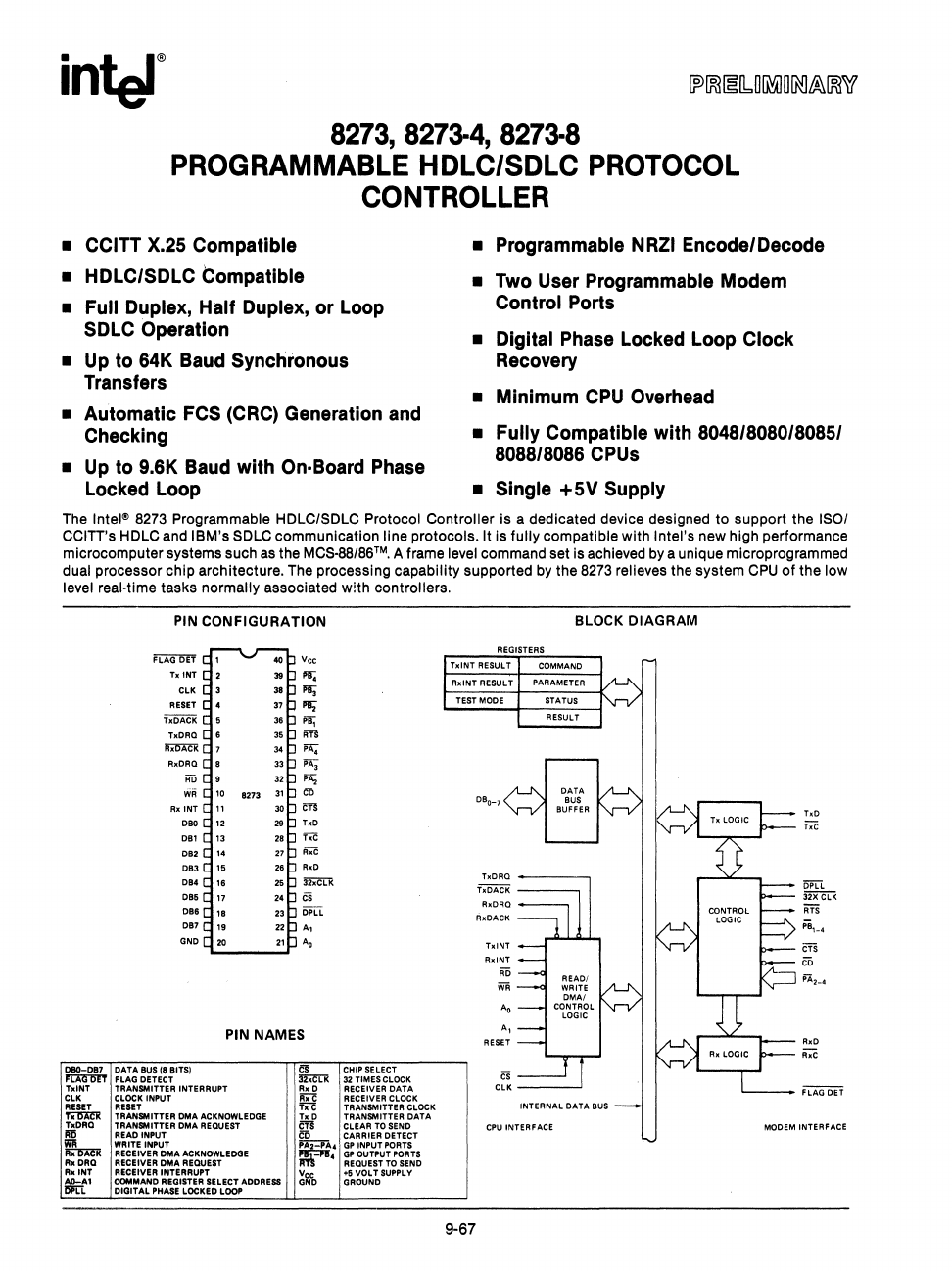

PIN

CONFIGURATION

flAG

DET

Vee

Tx

tNT

1'1!;

eLK

l'I3

RESET

l'I3

TxOACK

PT,

TxDRQ

;m

RxDACK

PA,

RxDRQ

PA,

R5

'A2

WR

CIl

R;I(

tNT

eTS

DB.

T,D

DB'

'fie

DB'

RiC

DB3

R,D

DB.

ffiC[K

DB'

cs

DBS

CPU

DB7

A,

GND

Ao

PIN

NAMES

DBO-DB7

DATA

BUS

fS

BITS)

~

FLAG

DETECT

TxtNT

TRANSMITTER

INTERRUPT

elK

CLOCK

INPUT

RESET

RESET

'fi"'OAfR

TRANSMITTER

DMA

ACKNOWLEDGE

TxORO TRANSMITTER DMA

REQUeST

1m

READ

INPUT

""

WRITE

INPUT

Ri"'5ACR'

RECEIVER

DMA

ACKNOWLEDGE

Ax

ORO

RECEIVER DMA

REQUEST

Ax

INT

RECEIVER

INTERRUPT

AD-A1 COMMAND REGISTER SELECT ADDRESS

lSISLL

DIGITAL

PHASE

LOCKED

LOOP

CS

CHIP SELECT

Him

32

TIMES

CLOCK

Alt 0 RECEIVER

DATA

Ax

C

RECEIVER

CLOCK

r"

C

TRANSMITTER

CLOCK

Tx 0 TRANSMITTER OATA

rn

CLEAR

TO

SEND

co

CARRIER DETECT

~:2-::4

GP

INPUT PORTS

m-

4

~~g~::~~6~:~~

Vee

+5

VOL T SUPPLY

GND GROUND

BLOCK OIAGRAM

08

0

-

7

T,D

r;c

TxDRQ

TxDACK

DPLL

32XCiJ(

RTs

RxDACK

PB'_4

TxlNT

ffi

RxlNT

Co

WR

PA

2

_

4

Ao

A,

RESET

R,D

R;C

cs

f'lAGDET

CPU

INTERFACE

MODEM INTERFACE

9-67