8355* /8355-2**

16,384·8IT ROM WITH

110

*Directly Compatible with 8085A CPU

**Directly Compatible with 8085A-2

• 2048 Words x 8 Bits

• Each

\/0

Port Line Individually

Programmable

as

Input or Output

• Single

+

5V

Power Supply

•

Internal Address Latch

• Multiplexed Address and Data Bus

• 2 General Purpose 8·Bit

\/0

Ports • 40·Pin DIP

The Intel® 8355

is

a ROM and

I/O

chip to be used in the MCS-85'·

microcomputer

system. The ROM portion is organized

as

2048 words by 8 bits. It has a maximum access time

of

400 ns to permit use with no wait states in the 8085A CPU.

The

1/0

portion

consists

of

2 general purpose

1/0

ports. Each

1/0

port has 8 port lines, and each 1/0

port

line

is

indivdu

o

ally

programmable as

input

or

output.

The 8355-2 has a 300ns access time

for

compatibility

with

the 8085A-2 microprocessor.

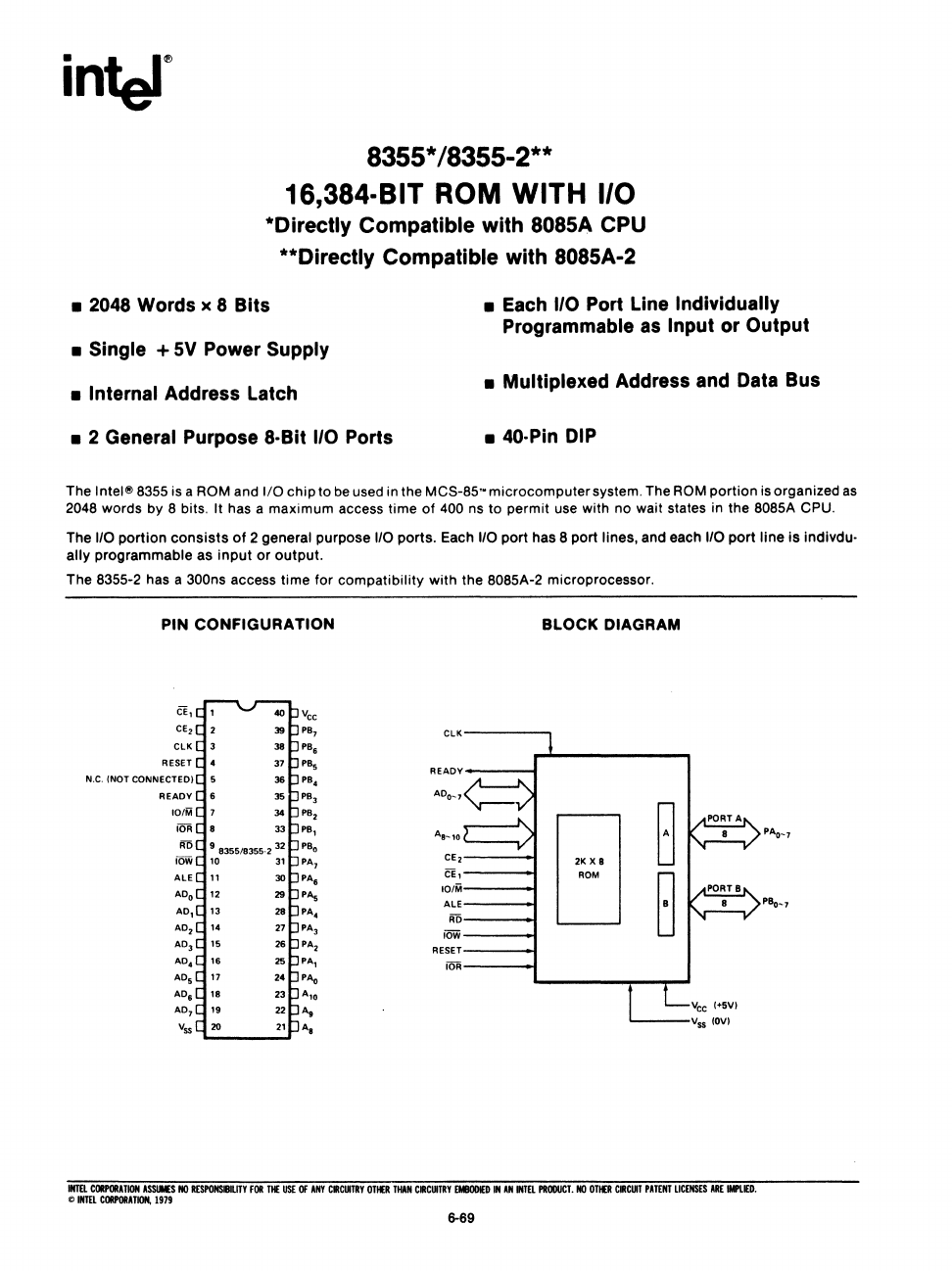

PIN

CONFIGURATION

BLOCK DIAGRAM

Vee

PB,

elK

PB,

RESET

PB,

READY

N.C. (NOT CONNECTED)

5

PB,

PB,

AD

o

_

7

PB,

~

PB,

A

B

-

10

RD

PB.

lOW

PA,

eE,

G

PA,

CE,

ROM

~

AD.

PAs

101M

ALE

AD,

PA,

RD

lOW

AD,

PA,

RESET

AD,

PA,

iDA

AD,

PAD

AD,

AD,

Vee

(+5VI

VSS

Vss

fOV)

INT£l

CORPORATION

ASSlHS

NO

RESPONSIBIlITY

FOR

THE

USE

OF

ANY

CIRCUITRY

OTHER

THAN

CIICUITRY

EMBOOIEO

IN

AN

IIITEl

PROOOCT.

NO

OTItER

CIRCIIIT

PATENT

LICENSES

ARE

IMPLIED.

"INTEL

CORPORATION.

1979

6-69

PA

O

-

7

PB

O

-

1