inter

8031/8051/8751

i

J

TXD RXD TXD RXD TXD RXD

RXD TXD TXD RXD TXD RXD

8051 8051

6051

8051

8051 8051

A.

MULTI-80s1 INTERCONNECT

-HALF

DUPLEX

B.

MULTI-80s1 INTERCONNECT

-FULL

DUPLEX

Figure

2.7.

UART

Interfacing

Schemes

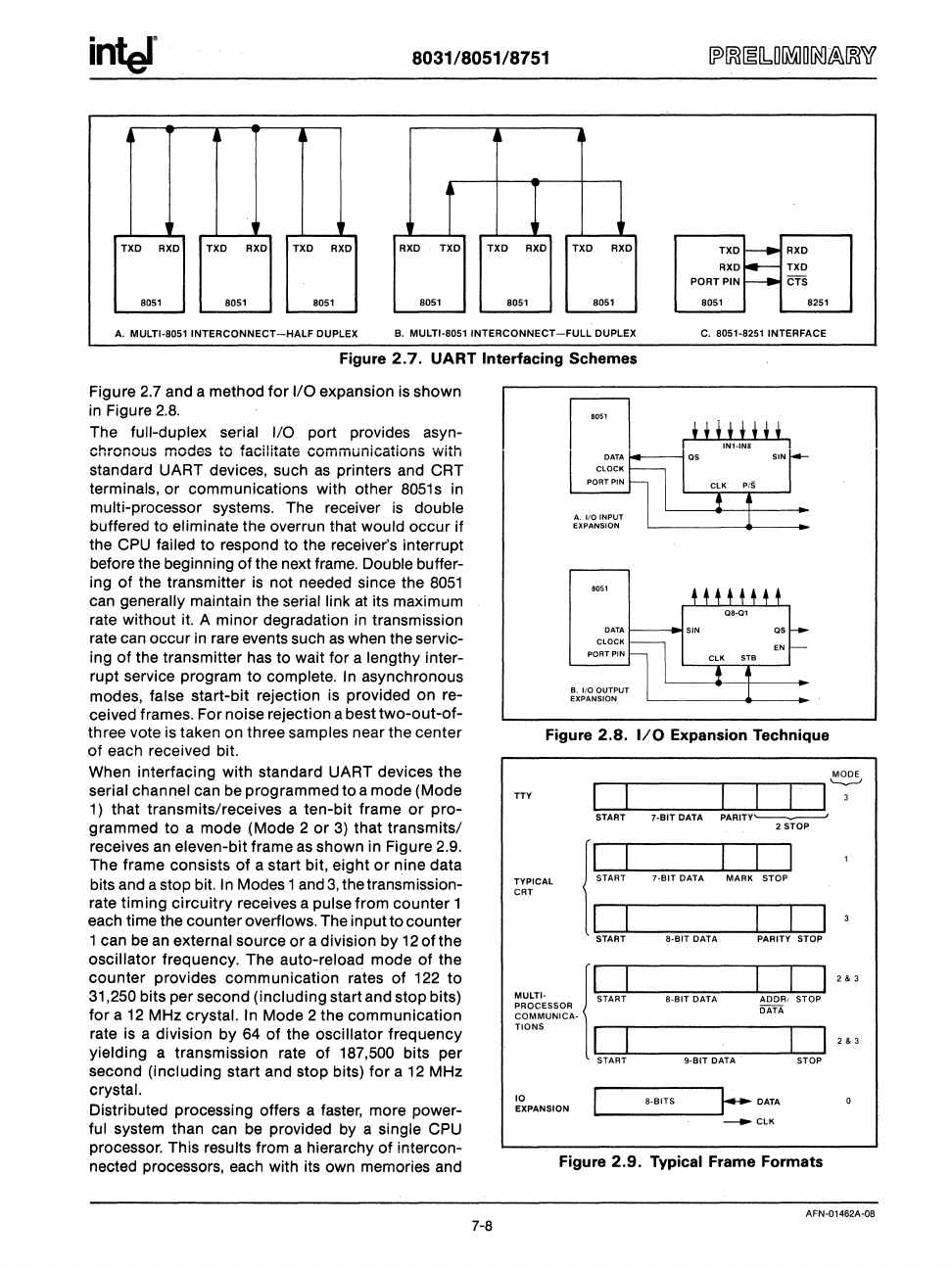

Figure 2.7 and a method

for

110

expansion is shown

in

Figure

2.8.

The full-duplex serial I/O port provides asyn-

chronous modes to

facilitate communications

'vvith

8051

DATA

CLOCK

PORT PIN

B.

1/0

OUTPUT

EXPANSION

TXD

-

RXD

RXD

~

TXD

PORT PIN

CTS

8051

8251

C.

8051-8251 INTERFACE

os

EN

standard UART devices, such

as

printers and CRT

terminals, or communications with other

8051s

in

multi-processor systems. The receiver

is

double

buffered

to

eliminate the overrun that would occur if

the CPU

failed to respond to the receiver's interrupt

before the beginning of the next frame.

Double buffer-

ing

of

the transmitter

is

not needed since the

8051

can generally maintain the serial link

at

its maximum

rate without it. A minor degradation

in

transmission

rate can occur

in

rare events such

as

when the servic-

ing

of

the transmitter has to wait for a lengthy inter-

rupt service program

to

complete.

In

asynchronous

modes,

false start-bit rejection

is

provided on re-

ceived frames. For noise rejection a best

two-out-of-

three vote is taken on three samples near the center

of

each received bit.

Figure

2.8.

1/0

Expansion Technique

When interfacing with standard UART devices the

serial channel can

be

programmed to a mode (Mode

1)

that transmits/receives a ten-bit frame

or

pro-

grammed to a mode (Mode 2

or

3)

that transmits/

receives an

eleven-bit frame

as

shown in Figure 2.9.

The frame consists

of

a start bit, eight

or

nine data

bits and a stop bit.

In Modes 1 and

3,

the transmission-

rate timing

circuitry

receives a pulse from counter 1

each time the counter

overflows. The input

to

counter

1 can

be

an external source

or

a division

by

12

of the

oscillator frequency. The auto-reload mode of the

counter provides communication rates

of

122

to

31,250 bits per second (including start and stop bits)

for

a

12

MHz crystal. In Mode 2 the communication

rate

is

a division by 64

of

the oscillator frequency

yielding a transmission rate

of

187,500 bits per

second

(including start and stop bits)

for

a

12

MHz

crystal.

Distributed processing offers a faster, more power-

ful system than can be provided by a single CPU

processor. This

results from a hierarchy

of

intercon-

nected processors, each with its own memories and

7-8

MODE

TTY

I

I~

START

7·BIT

DATA

PARITY~

2

STOP

{"

TYPICAL

START

7-81T

DATA

MARK

STOP

CRT

I I I

START

8-BIT DATA

PARITY STOP

r I

I

2&3

MULTI- STAAT

8-BIT

DATA

ADDRi

STOP

PROCESSOR

DATA

COMMUNICA-

TIONS

I I

2 & 3

START

9·BIT

DATA

STOP

10

S-BITS

~DATA

EXPANSION

---...

eLK

Figure

2.9.

Typical Frame

Formats

AFN-01462A-08