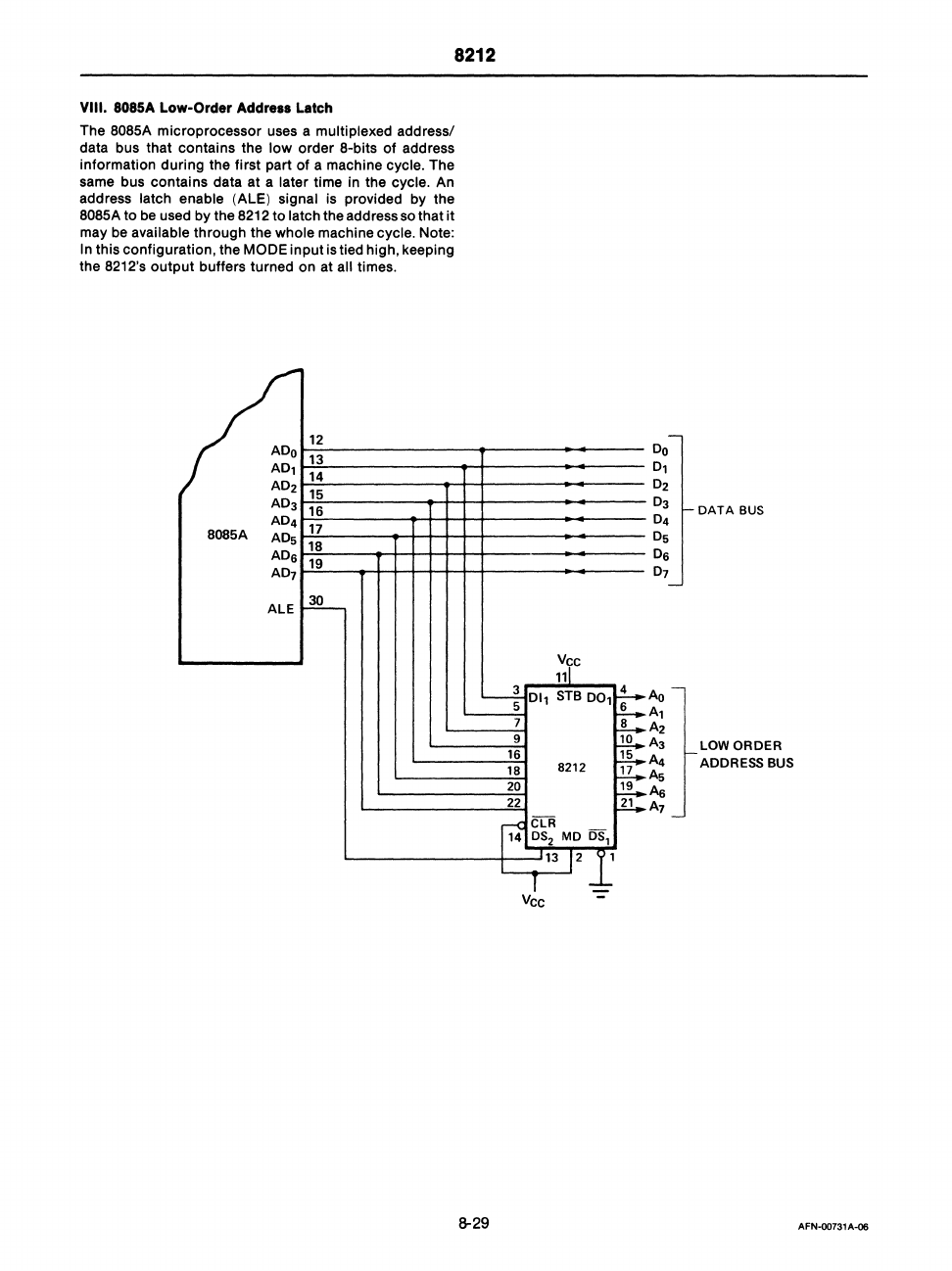

VIII. 808SA Low-Order Address Latch

The

808SA

microprocessor uses a multiplexed address/

data bus that contains the

low order 8-bits of address

information during the first part of a machine

cycle. The

same bus contains data at a

later time in the cycle. An

address

latch enable (ALE) signal is provided by the

808SA

to

be

used by the 8212 to latch the address so that it

may be

available through the whole machine cycle. Note:

In

this configuration, the MODE input is tied high, keeping

the 8212's output buffers turned on at

all times.

12

/:

13

AD,

14

AD2

1S

AD3

16

AD4

17

BOSSA

AD5

AD6

18

19

AD7

ALE

~

8212

..

VJc

11

~DI,

STBDO,&

5

~

7

8

9

~

16

~

18

8212

f-j7

20

r,g-

22 _

121:

f

CLR

"

.';,

j~

1

1 _

Vcc

8-29

DATA

BUS

LOW ORDER

ADDRESS BUS

AFN-00731 A-()6