8259A

OPERATION

COMMAND

WORDS

(OCWs)

After the Initialization Command Words (ICWs) are pro-

grammed Into the 8259A, the chip Is ready

to

accept

Interrupt requests at Its Input lines. However, during the

8259A operation, a selection

of

algorithms can com-

mand the 8259A

to

operate

In

various modes through

the Operation

Command Words (OCWs).

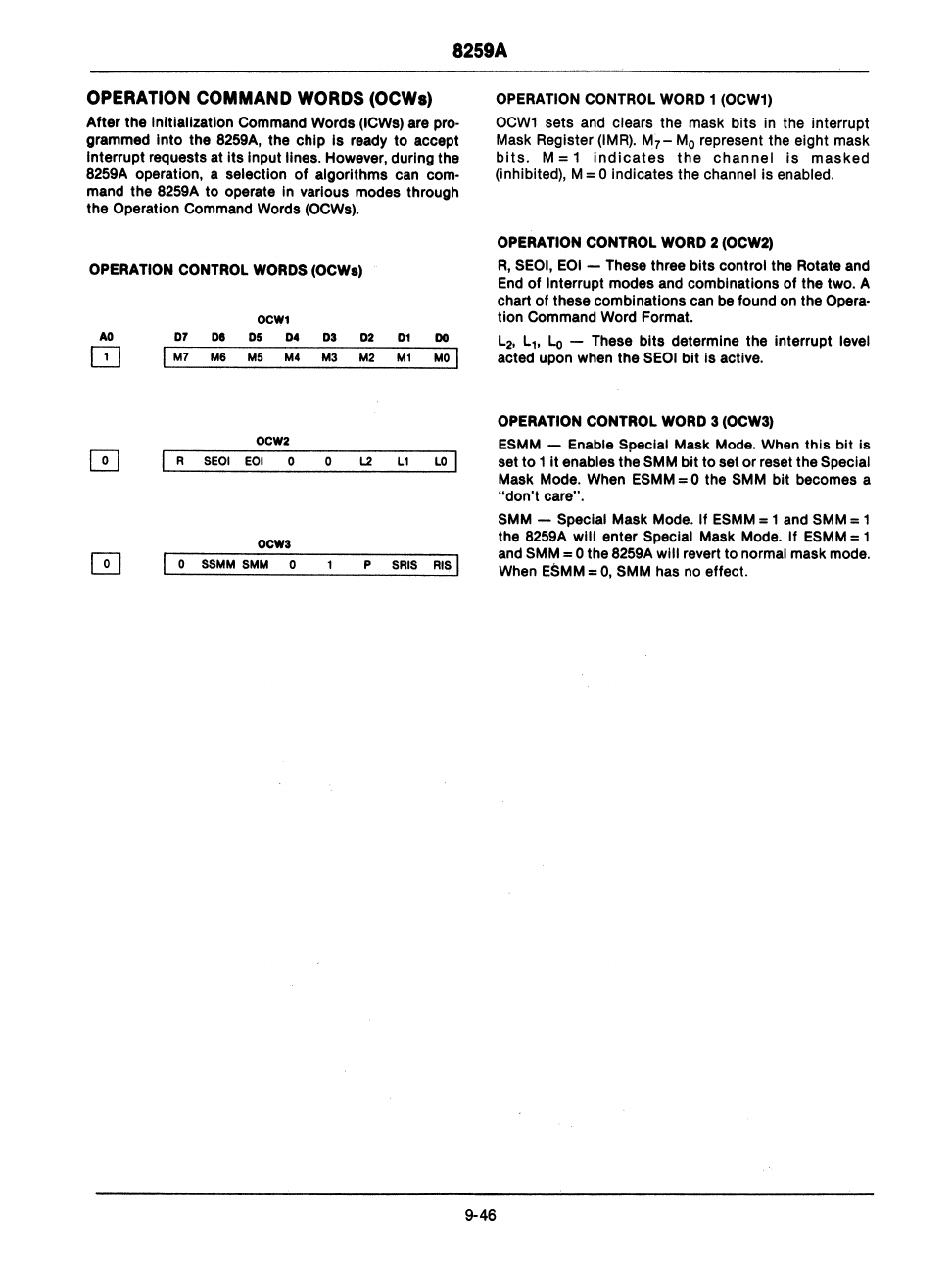

OPERATION CONTROL

WORDS

(OCWI)

OCW1

AO

D7

De

D5

D4 D3 D2

D1

DO

[i]

I M7 Me M5 M4 M3 M2

M1

MO

I

OCW2

0

I R

SEOI

EOI

0 0

L2

Ll

LOI

ocwa

0

I 0

SSMM SMM

0

P SRIS

RIS

I

OPERATION CONTROL

WORD

1

(OCW1)

OCW1

sets and clears the mask

bits

In

the Interrupt

Mask Register

(IMR).

M:'-

Mo

represent the eight mask

bits.

M = 1

Indicates

the

channel

is

masked

(Inhibited), M = 0 indicates the channel

is

enabled.

OPERATION CONTROL WORD 2

(OCW2)

R,

SEOI,

EOI

- These three

bits

control the Rotate and

End

of

Interrupt modes and combinations

of

the two. A

chart

of

these combinations can be found on the Opera·

tlon Command Word Format.

L

2

,

L

1

,

La

- These

bits

determine the Interrupt level

acted upon when the

SEOI

bit Is active.

OPERATION CONTROL

WORD

3

(OCW3)

ESMM

- Enable Special Mask Mode. When this

bit

Is

set

to

1

It

enables the SMM bit

to

set

or

reset the Special

Mask Mode. When

ESMM

= 0 the SMM bit becomes a

"don't

care".

SMM - Special Mask Mode. If

ESMM

= 1 and SMM = 1

the 8259A will enter

Special Mask Mode.

If

ESMM

= 1

and

SM

M = 0 the 8259A will revert to normal mask mode.

When

ESMM

=

0,

SMM has no effect.

9-46