inter

8214/3214*

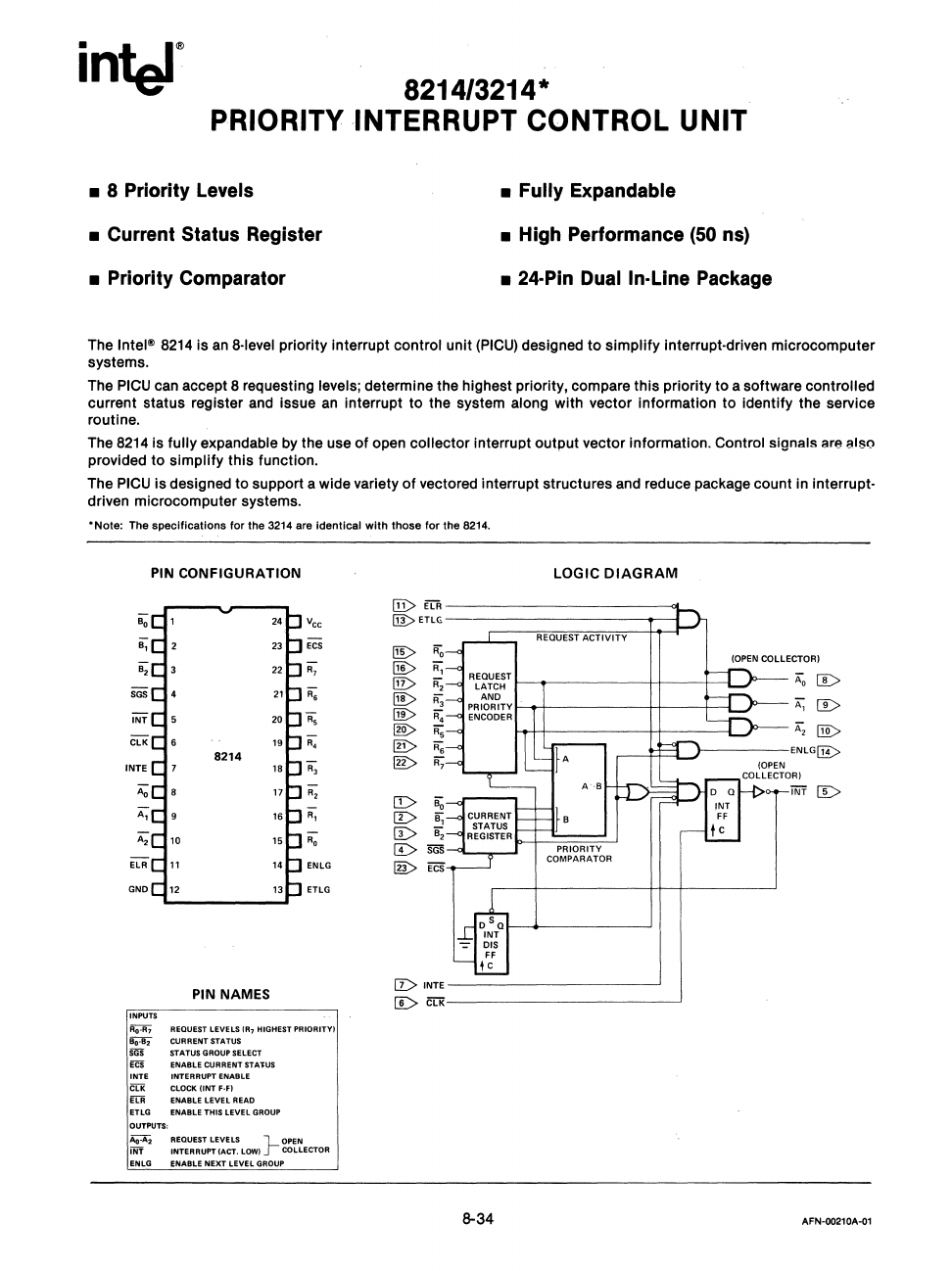

PRIORITY INTERRUPT CONTROL UNIT

• 8 Priority Levels

• Fully Expandable

• Current Status Register • High Performance

(50

ns)

• Priority Comparator • 24·Pin Dual In·Llne Package

The

Intel~

8214

is

an

8·level priority Interrupt control unit

(PICU)

designed

to

simplify interrupt·driven microcomputer

systems.

The

PICU

can accept 8 requesting levels; determine the highest priority. compare this priority to a software controlled

current status register and issue

an

interrupt

to

the system along with vector information

to

identify the service

routine.

The

8214

is fully expandable

by

the use

of

open collector interrupt output vector information. Control signals are also

provided

to

simplify this function.

The

PICU

is designed to support a wide variety

of

vectored interrupt structures and reduce package count in Interrupt·

driven microcomputer systems.

'Note:

The specifications for the

3214

are Identical

with

those

for

the

8214.

PIN

CONFIGURATION

·0

Vee

.,

Ees

.,

A;

SGS

A,

'NT

R,

elK

A,

8214

R,

'NTE

A;;

A,

A,

A,

A,

R,

ElA

ENLG

GNO

ETLG

PIN

NAMES

INPUTS

RO-A?

REQUEST LEVELS IR7 HIGHEST PRIORITY)

80-82

CURRENT

STATUS

iGi

STATUS

GROUP

SELECT

ECi

ENABLE CURRENT STA'JUS

INTE INTERRUPT ENABLE

ill

CLOCK

UNT

F·FI

ELA

ENABLE

lEVEL

READ

ETLG

ENABLE

THIS

LEVEL

GROUP

OUTPUTS:

.....

,

M

ENLO

REQUEST

LEvl:LS

}-OPEN

INTEARUPT(ACT.

LOW)

COLLECTOR

ENABLE

NEXT

LEVEL GROUP

IE>

ElR

I1!>ETlG--

~

Ra

I!!>

R;

[!D

R,

I!!>

R,

I!!>

;;:;

~

"-

~

As

~

R;

I:!>

B,

ID

s:;

II>

B,

[D

SGS

l?D

EcS

LOGIC DIAGRAM

REQUEST

ACTIVITY

PRIOR

lTV

COMPARATOR

CC>'NTE-----------------~

OC>

~--------------------------~

8-34

A.[D

iI,[D

A,11!>

AFN·00210A-ol