8291

Setting the

"ton"

bit generates the local ton (talk-only)

. message and sets the

8291

to a talk-only mode. This mode

allows the device

to

operate

as

a talker in

an

interface

system without a controller.

Setting

the

"Ion"

bit

generates the local Ion (listen-only)

message and sets the

8291

to

a listen-only mode. This

mode allows the device to operate

as

a listener in

an

interface system

without

a controller.

The mode

of

addressing implemented by the

8291

may be

selected by writing one

of

the following bytes to the

Address Mode Register:

Register Contents

10000000

01000000

11000000

00000001

00000010

00000011

Mode

Enable talk only mode (ton)

Enable listen only mode (Ion)

The

8291

may talk to itself

Mode

1,

(Primary-Primary)

Mode 2 (primary-Secondary)

Mode 3 (primary/APT-Primary/APT)

The Address Status Registercontains information used by

the microprocessor to handle its own addressing. This

information includes status bits that monitor the address

state

of

each talker/listener,

"ton"

and "Ion" flags which

indicate the talk

only

and listen

only

states, and

an

EOI bit

which, when set, signifies that the END message came

with the last data byte.

LPAS and TPAS indicate that the

listener or talker primary address has been received. The

microprocessor can then use these bits when the

secondary address is passed through to determine

whether the

8291

is addressed to talk or listen. The LA

(listener addressed) bit will

be

set when the

8291

is in

LACS (Listener Active State)

or

in LADS (Listener

Addressed State). Similarly, the TA (Talker Addressed bit

will

be

set

to

indicate TACS

or

TAOS, but also

to

indicate

SPAS (Serial Poll Active State). The MJMN bit

is

used to

determine whether the information in the other bits

applies to the Major

or

Minor

talker/listener.

It

is set to "1"

when the

Minor

talker/listener

is

addressed. It should be

noted that

only

one talker/listener may

be

active at any

one time. Thus, the MJMN bit will indicate which, if either,

of

the talker/listeners

is

addressed

or

active.

The Address 0/1 Register is used for specifying the

device's addresses according

to

the format selected in

the Address Mode Register. Five bit addresses may be

loaded into the Address

0 and Address 1 registers by

writing into the Address

0/1

Register. The ARS bit is used

to

select which

of

these registers the other seven bits will

be loaded into. The DT 'and DL brts may be used to disable

the talker

or

lis.tener function at the address Signified by

the other five bits. When

Mode.l

addressing is used and

only

one primary address is desired, both the talker and

the listener should

be

disabled at the

Minor

address.

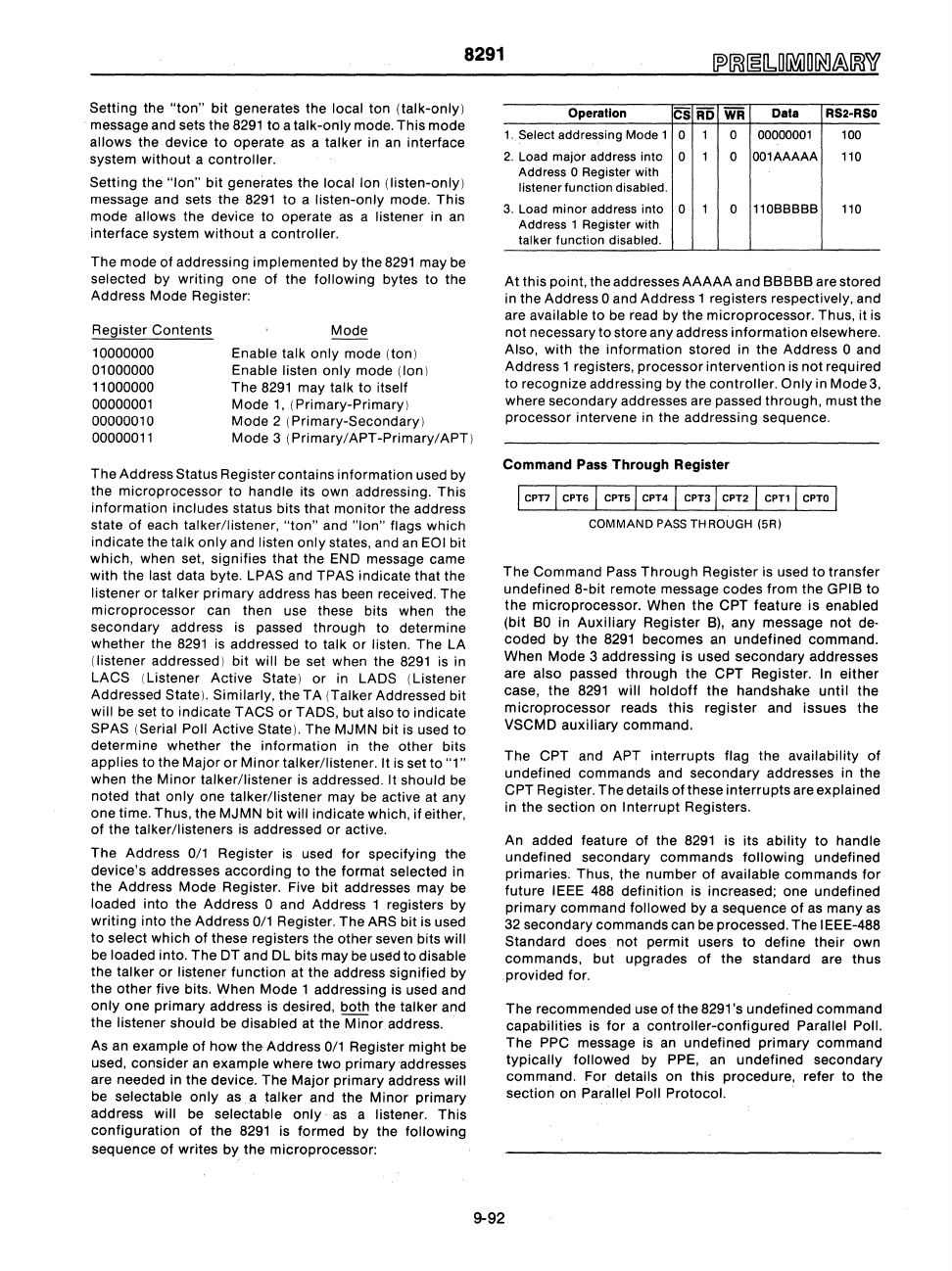

As an example

of

how

the Address

0/1

Register might be

used, consider

an

example where

t.wo

primarY'addresses

are

.needed in the device. The Major primary address will

be selectable

only

ass

lalker

and the

Minor

primary

address will be selectable

only·

as

a listener. This

configuration

of

the

8291

is fo.rmed by the following

sequence

of

writes

by.

the microprocessor:

Operation

CS RD WR

Data

RSZ-RSO

1

..

Select addressing Mode 1

0

1

0

00000001 100

2.

Load major address

into

0

1

0

001AAAAA

110

Address 0 Register with

listener function disabled.

3.

Load

minor

address into 0 1 0 110BBBBB 110

Address 1 Register with

talker function disabled.

At

this point, the addresses AAAAA and BBBBB are stored

in the Address

0 and Address 1 registers respectively, and

are available to

be

read by the microprocessor. Thus, it

is

not necessary to store any address information elsewhere.

Also, with the information stored in the Address

0 and

Address 1 registers, processor intervention is not required

to

recognize addressing by the controller. Only in Mode3,

where secondary addresses are passed through, must the

processor intervene in the addressing sequence.

Command

Pass

Through Register

I~I~I-I~I~I~I~I~I

COMMAND

PASS

THROUGH (5RI

The Command

Pass

Through Register is used to transfer

undefined 8-bit remote message codes from the

GPIB

to

the

microprocessor. When the CPT feature

is

enabled

(bit

BO

in Auxiliary Register

B),

any message

not

de-

coded by the

8291

becomes an undefined command.

When Mode 3 addressing

is

used secondary addresses

are also passed through the CPT Register.

In

either

case, the

8291

will

holdoff

the handshake

until

the

microprocessor

reads

this

register and issues the

VSCMD auxiliary command.

The CPT and APT interrupts flag the availability

of

undefined commands and secondary addresses in the

CPT Register. The details

of

these interrupts are explained

in the section on

Interrupt Registers.

An added feature

of

the

8291

is its

ability

to handle

undefined secondary commands following undefined

primaries: Thus, the number

of

available commands

for

future IEEE 488 definition is increased; one undefined

primary command followed by a sequence

of

as many as

32 secondary commands can be processed. The IEEE-488

Standard does. not permit users to define their own

commands, but upgrades

of

the standard are thus

.provided for.

9-92

The recommended use

o.f

the

8291

's undefined command

capabilities is

for

a controller-configured Parallel Poll.

The PPC message is

an

undefined primary command

typically followed by

PPE,

an undefined secondary

command. For details on this procedure, refer to the

section on

Parallel Poll Protocol. .